La mémoire physique

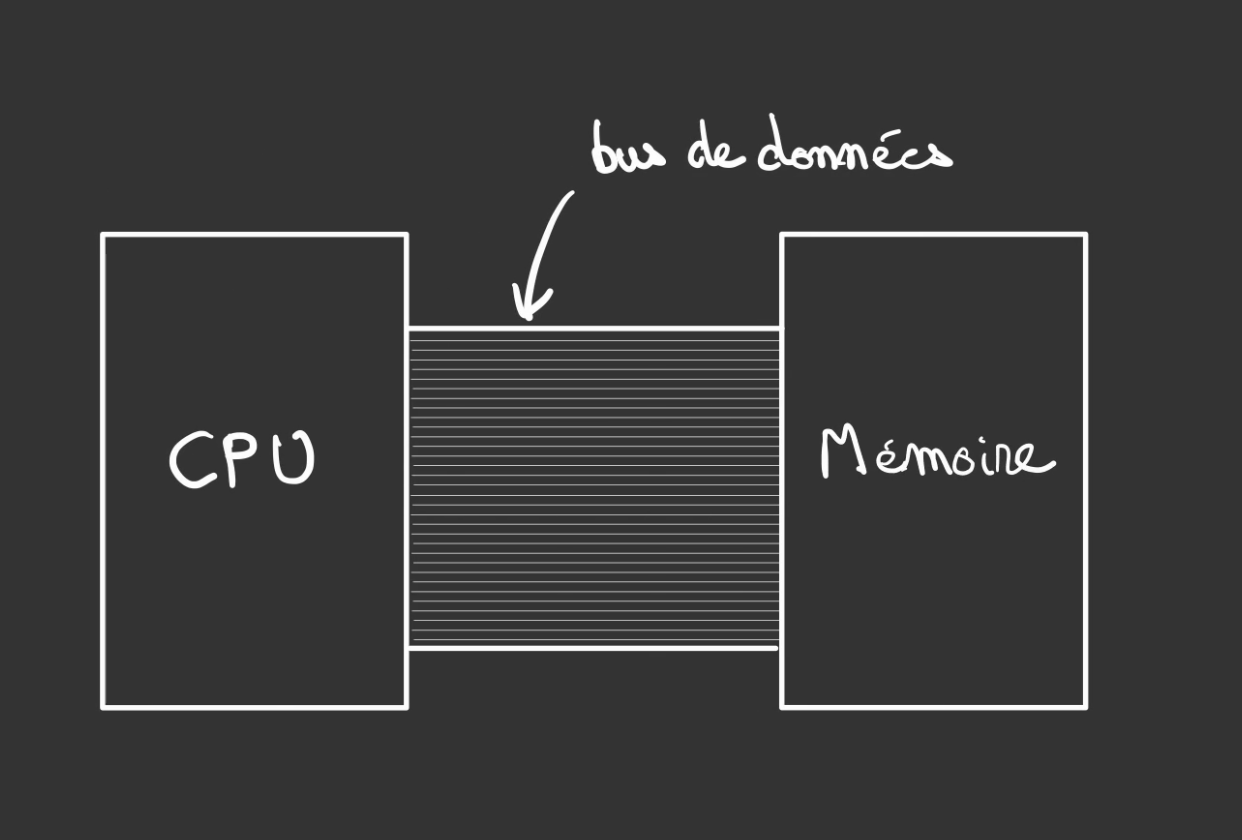

Architecture de Von Neumann

Tous les ordinateurs que vous utilisez aujourd'hui au quotidien sont basés sur une architecture à comprendre une manière d'agencer des composants et de les faire se parler.

Cette architecture se nomme von Neumann nommée d'après le nom du touche à tout John von Neunamm.

Il a été le premier à théoriser le concept de mémoire unique à la fois pour le programme et pour les données.

L'architecture se compose de 3 éléments principaux :

- Une unité de traitement appelée généralement CPU : elle réalise les traitements et les calculs sur les données

- Une mémoire : stocke les données du programme et le programme lui-même.

- Un bus de communication : un ensemble de fils de même longueur

L'architecture précédente séparait le programme de la donnée.

Elle s'appelait l'architecture Harvard. Plus compliqué à construire que son homologue du jour.

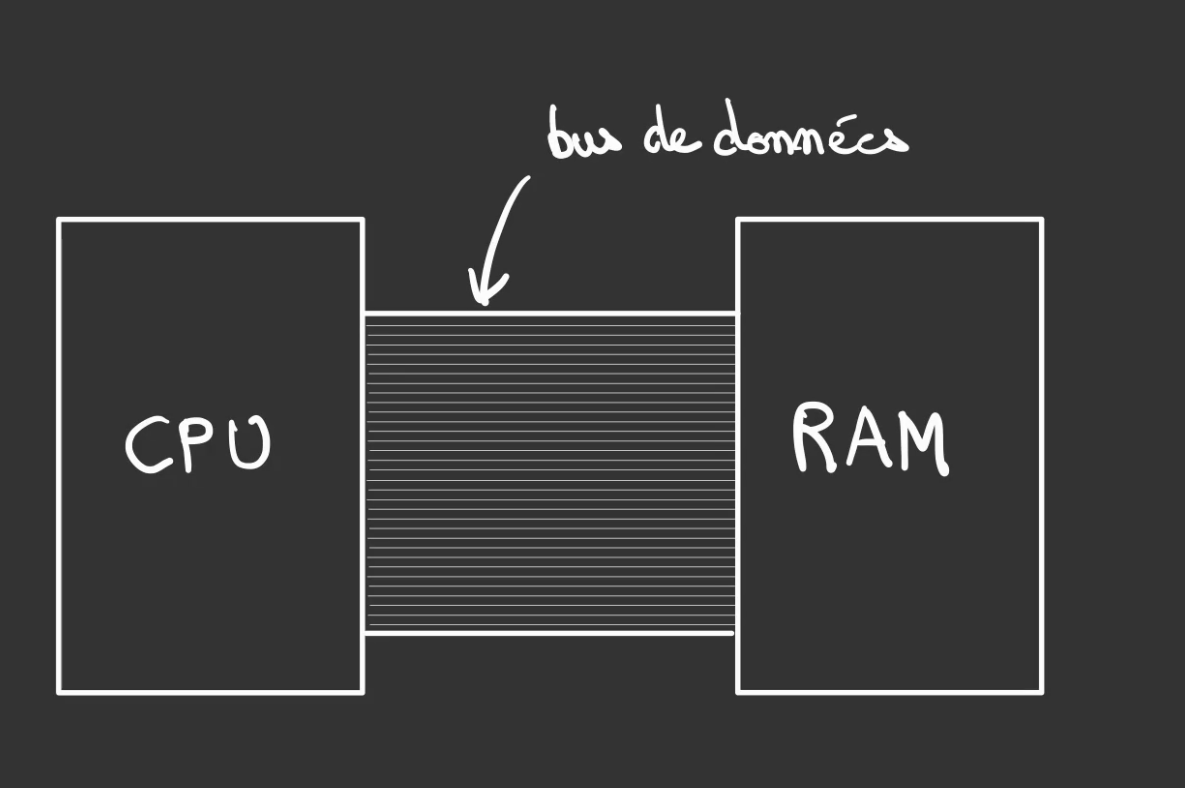

La RAM

Dans les ordinateurs de tous les jours, votre tour, le laptop, etc ...

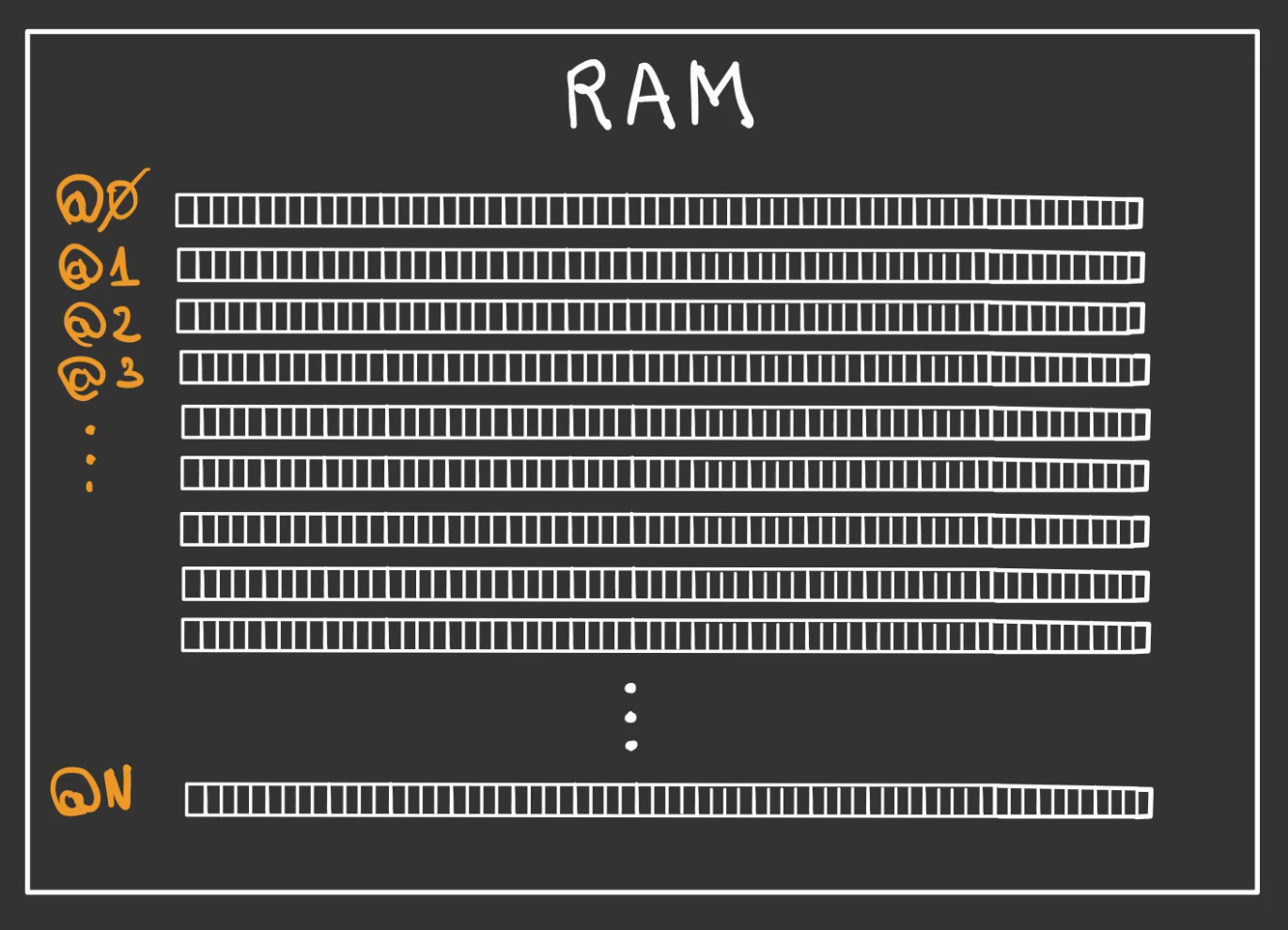

Le bloc de mémoire se nomme une RAM pour Random Access Memory.

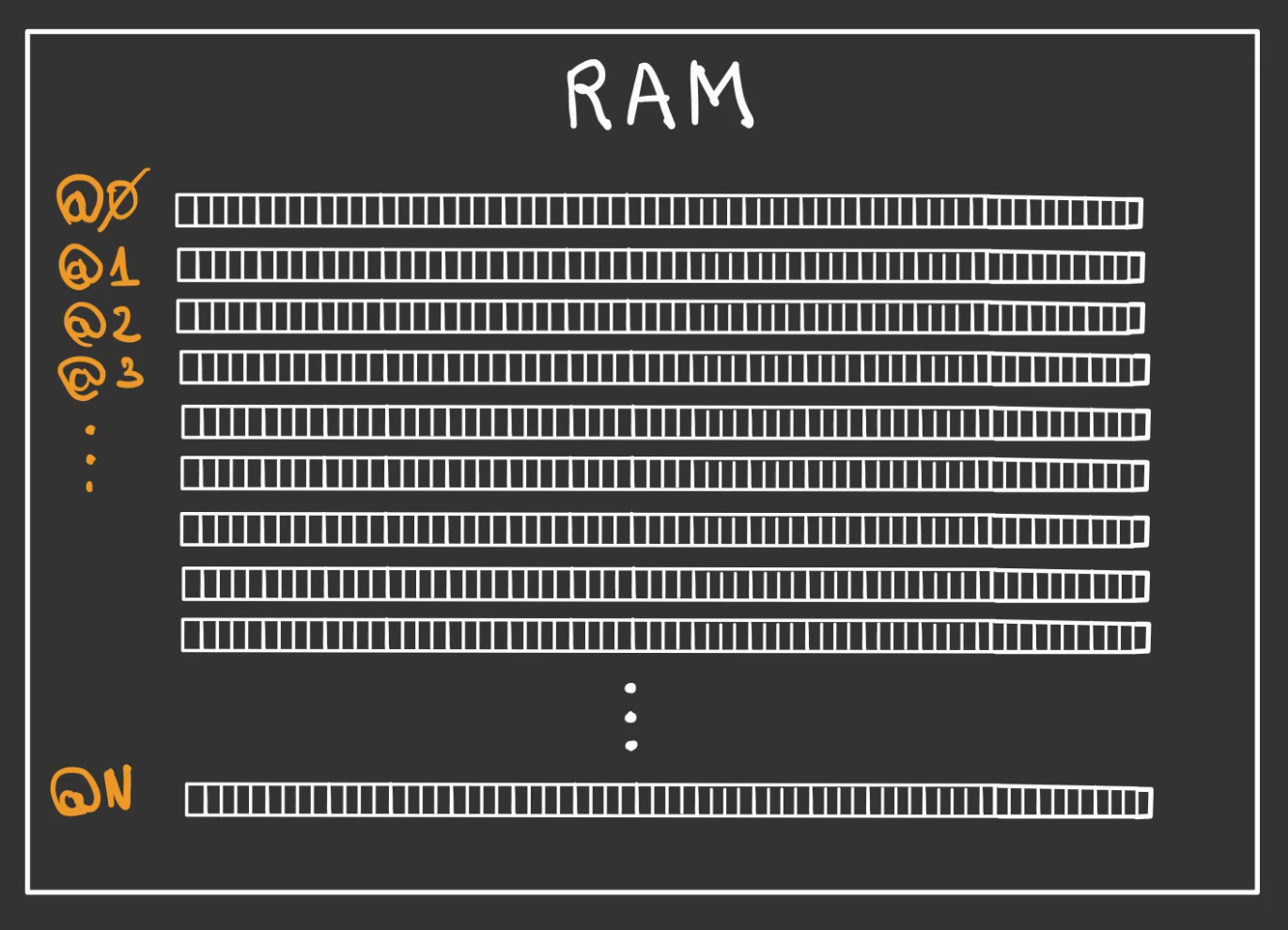

Si l'on zoom sur le bloc RAM, on s'aperçoit que celui est composé d'une série de lignes de blocs.

Chaque ligne est désignée par une adresse.

La première adresse étant @0 et la dernière @N.

N le nombre total de lignes dans la RAM.

Zoomons encore sur une ligne de blocs.

Chaque bloc est numéroté par rapport à sa position dans la ligne.

Arbitrairement, on choisit la droite comme étant l'origine, mais on pourrait totalement faire l'inverse.

Chaque bloc est appelé une cellule mémoire.

Continuons de descendre.

Cellule mémoire

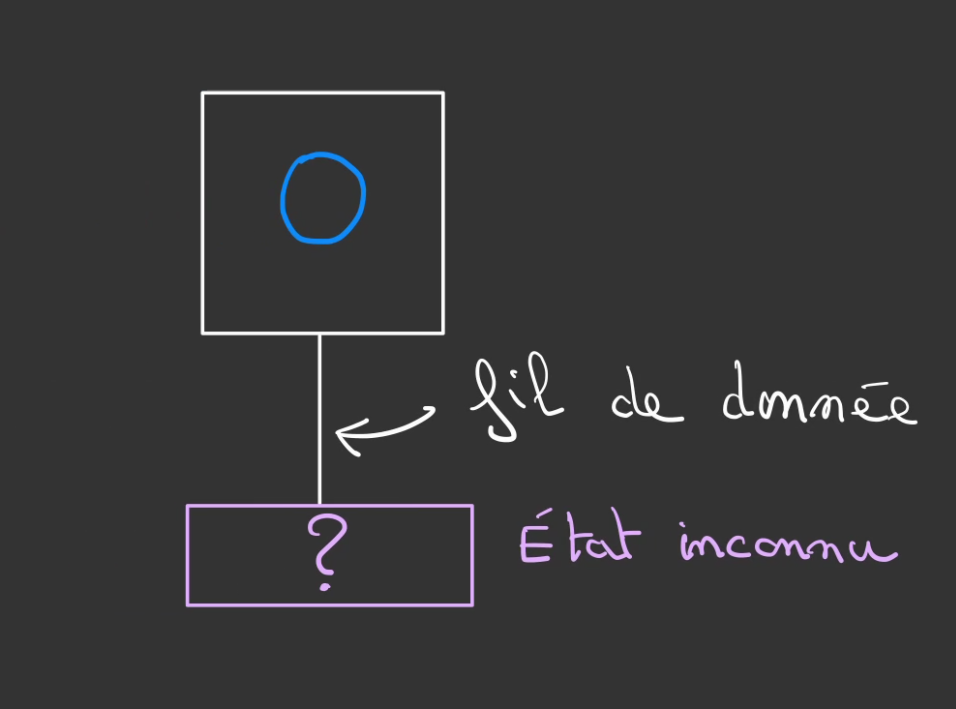

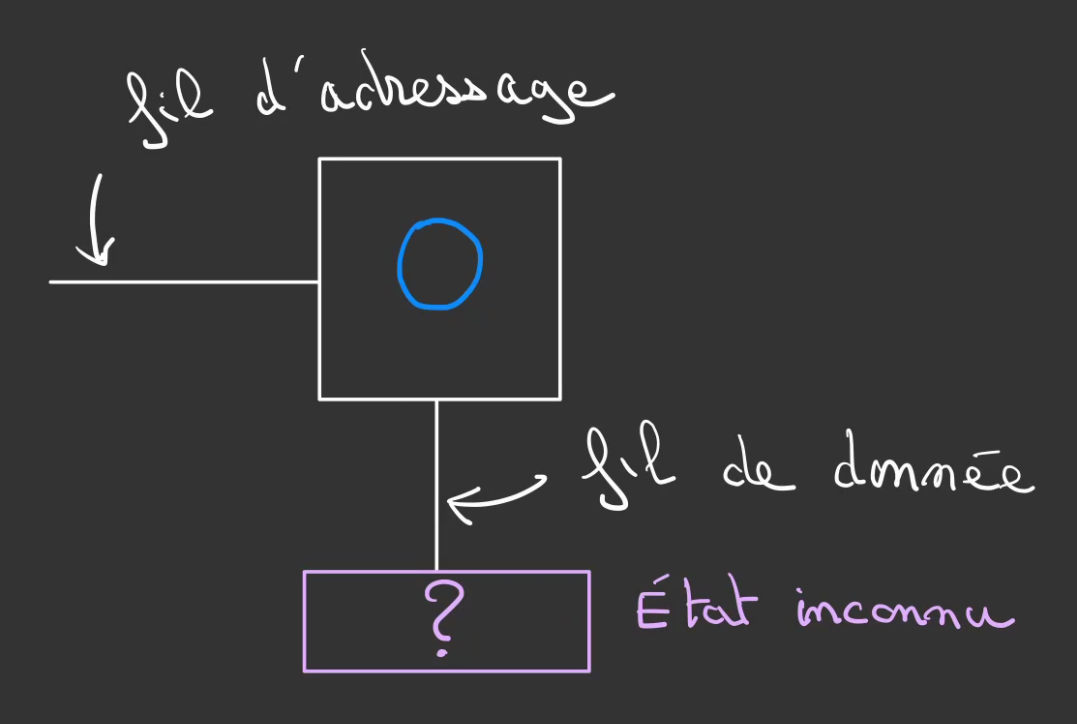

On est maintenant au niveau d'une cellule mémoire.

Il s'agit d'un bloc qui peut avoir deux états.

Un état 0 logique.

Un état 1 logique.

Il est possible de lire sa valeur.

Pour cela branche un fil de donnée à notre cellule.

Pour le moment la valeur stockée dans la cellule est inconnue de l'extérieur.

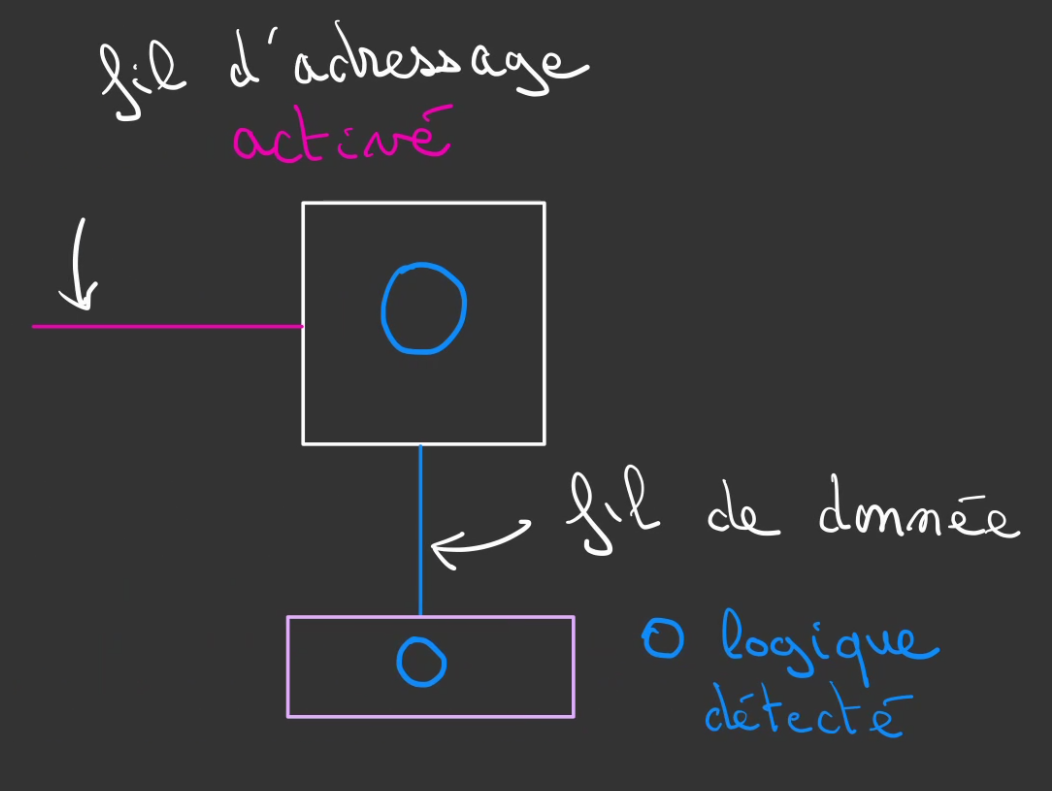

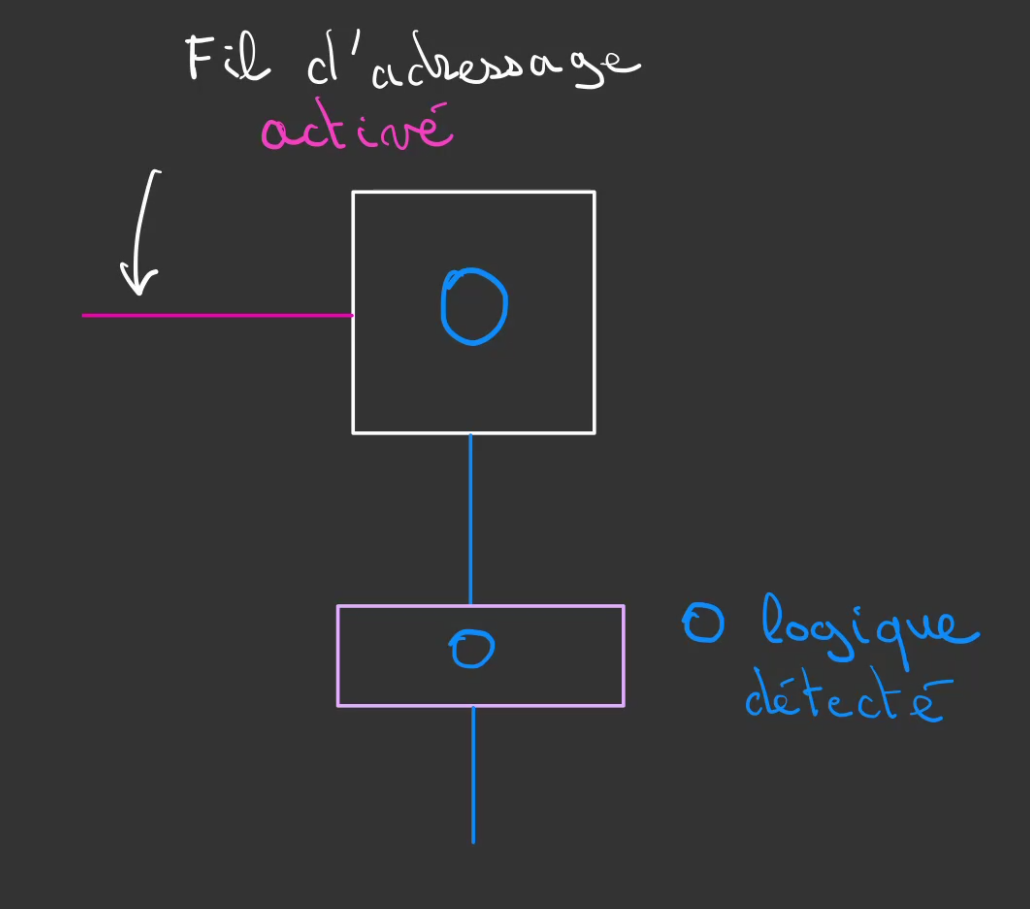

Pour pouvoir lire l'information contenue, il faut en quelque sorte activer la cellule.

Ceci est fait au moyen d'un second fil, appelé fil d'adressage.

Pour lire l'information, on vient activer le fil d'adressage.

Cela a pour effet d'extraire la donnée de la cellule qui se propage dans le fil de donnée, ici un état logique 0.

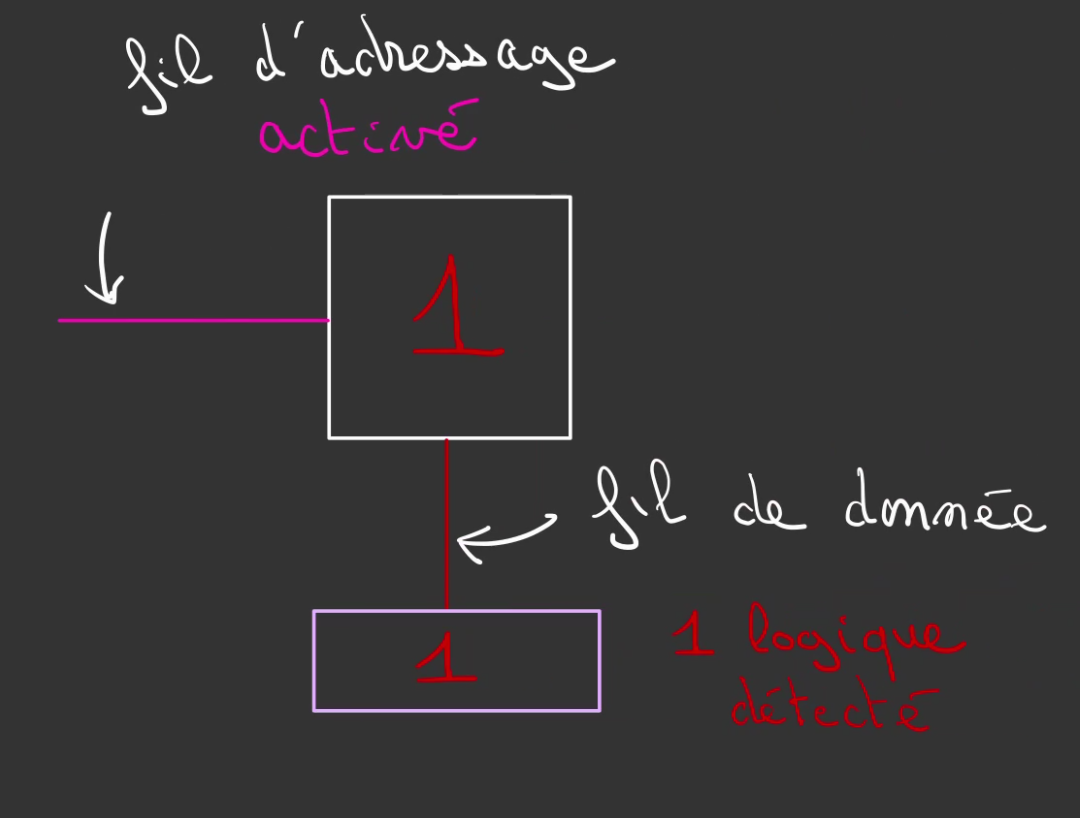

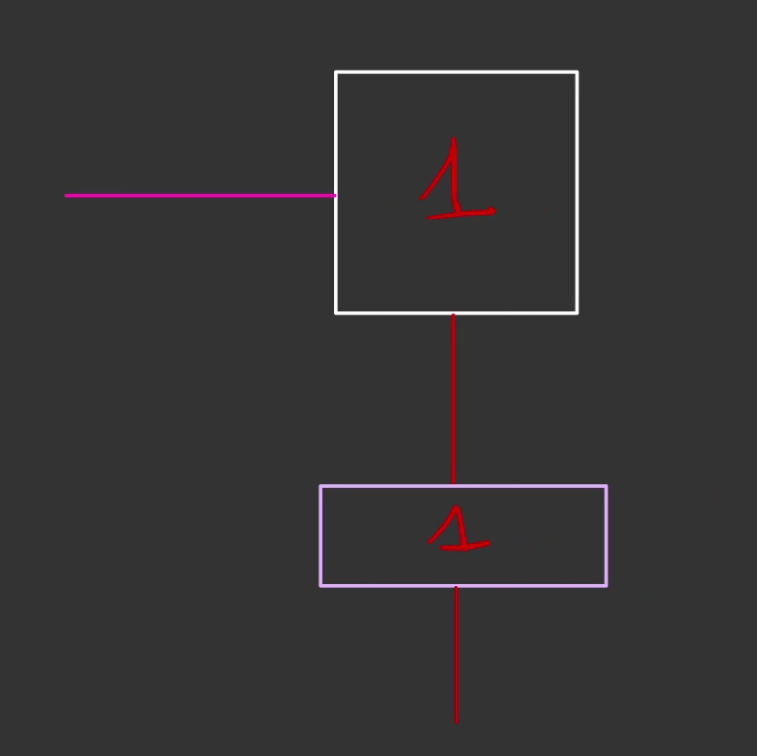

De la même manière si 1 logique est stocké, activer la cellule au travers du fil d'adressage permettra de récupérer ce 1 dans le fil de donnée.

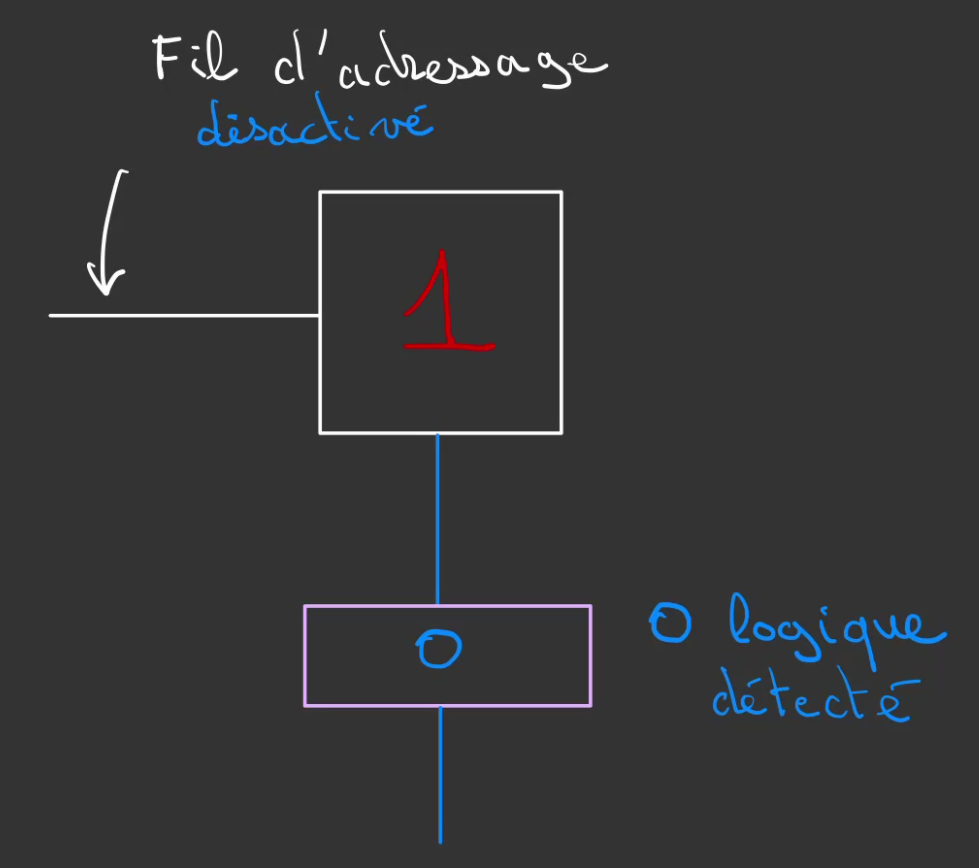

Il est possible d'imposer l'état de la cellule au travers du fil de donnée.

Mais tant que la cellule n'a pas été activée au travers du fil d'adressage, l'état de la cellule reste inchangée.

Pour cela, il faut activer le fil d'adressage, qui permet d'imposer l'état 0 à notre cellule.

Un fois le fil d'adressage désactivé notre cellule conserve son état 0.

De cet état 0, on peut alors venir appliquer l'état 1.

Lorsque le fil d'adressage se désactive, le 1 est conservé.

Mot binaire

Bon c'est cool on peut stocker 0 et 1 et les lire / écrire à notre convenance.

Mais on n'ira pas loin avec une seule cellule. 🙄

C'est ici qu'intervient la représentation binaire des nombres.

Dans notre système, on nomme bit une cellule mémoire.

bit : binary digit => deux états

Avec 2 bits, il est possible de représenter:

- 00 => 0

- 01 => 1

- 10 => 2

- 11 => 3

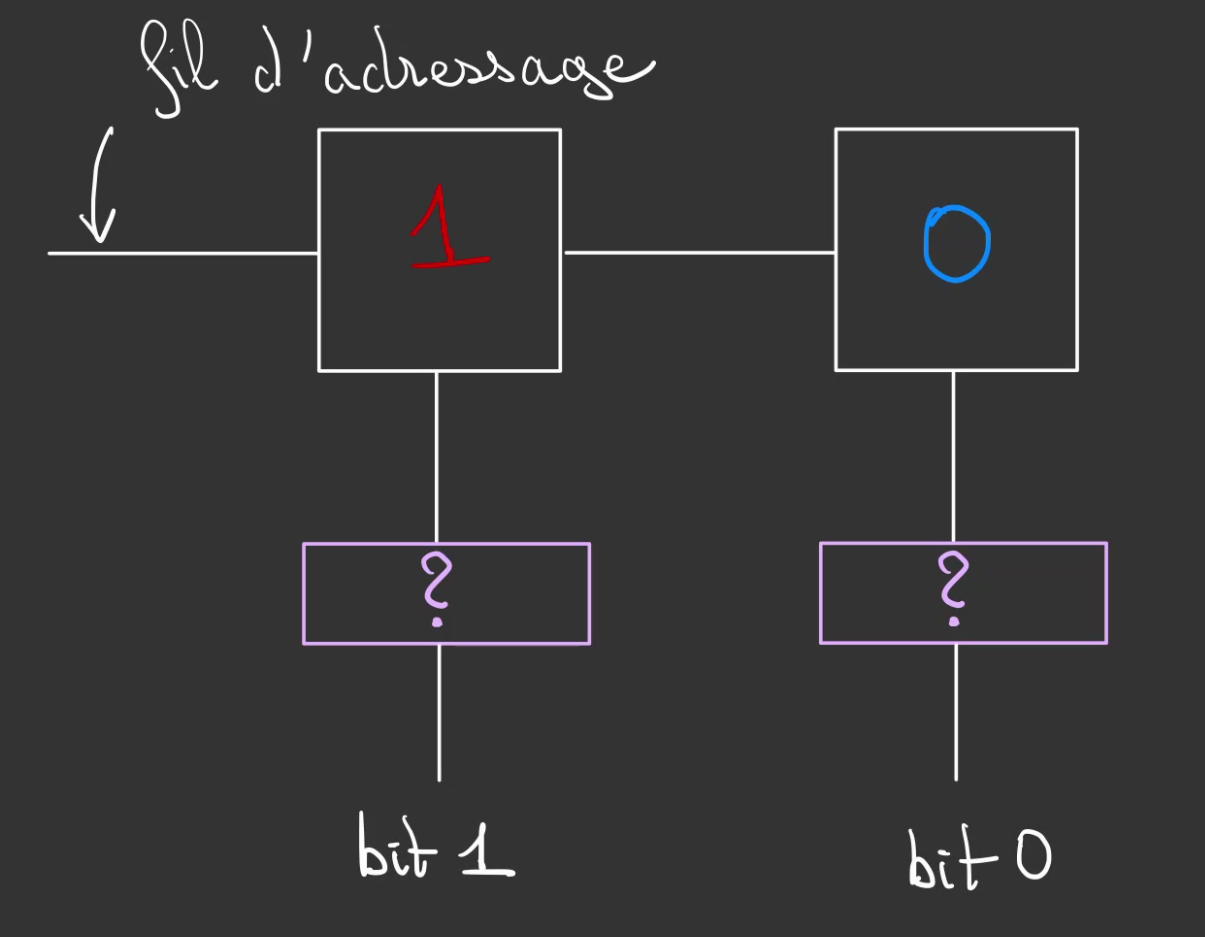

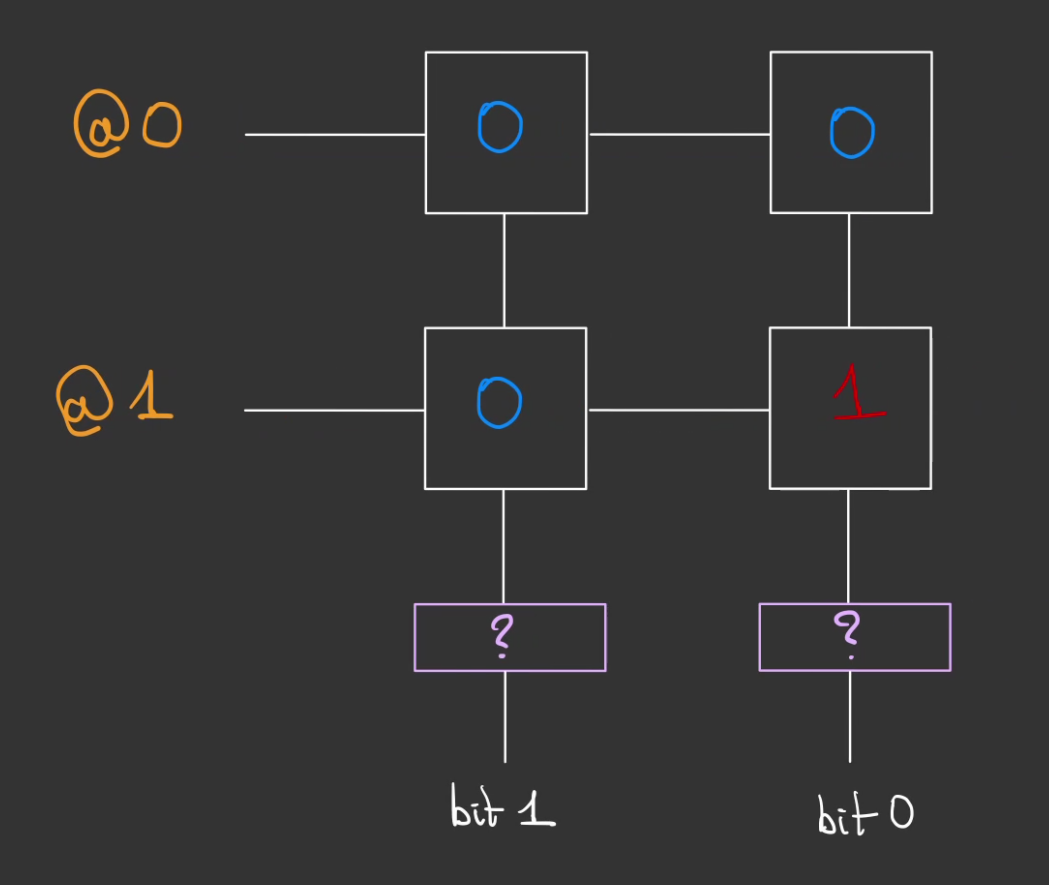

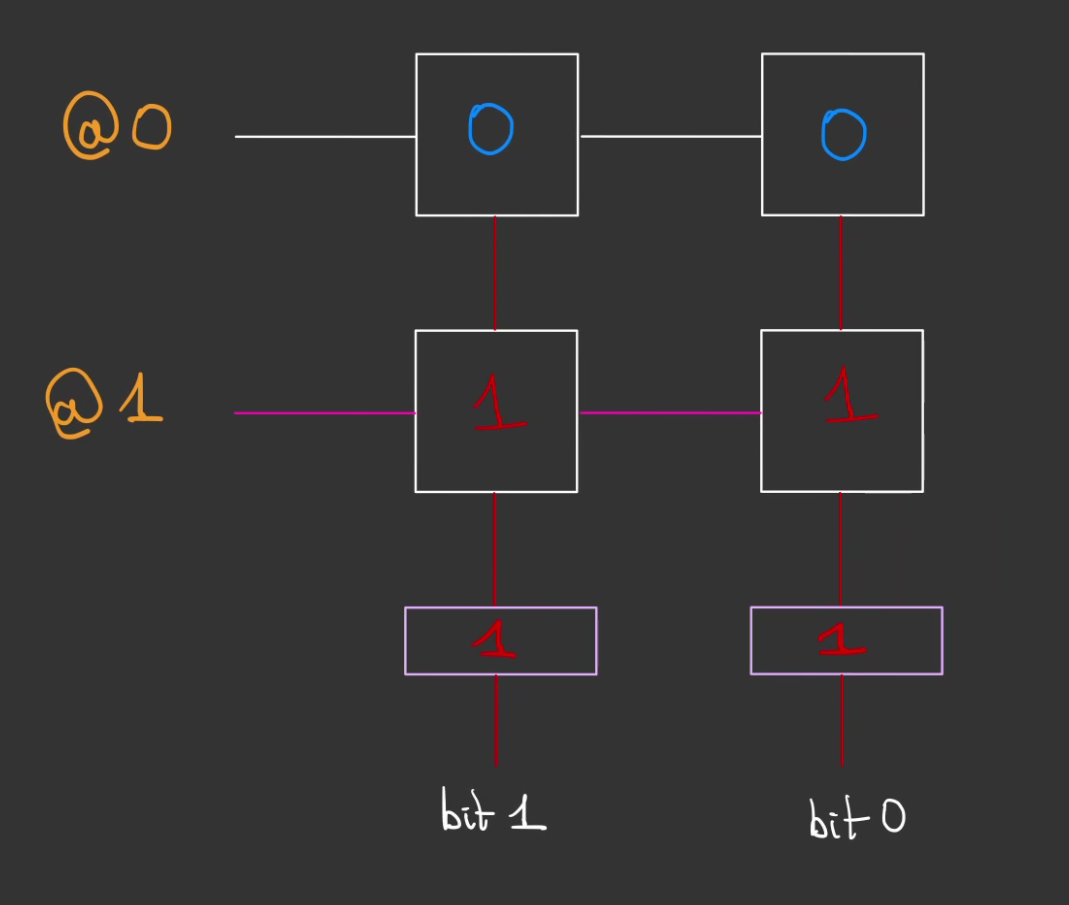

Nous allons donc agencer deux cellules pour pouvoir de manière indépendante, stocker les digits du nombre que l'on souhaite stocker.

Il est à remarquer que le fil d'adressage est commun au deux cellules.

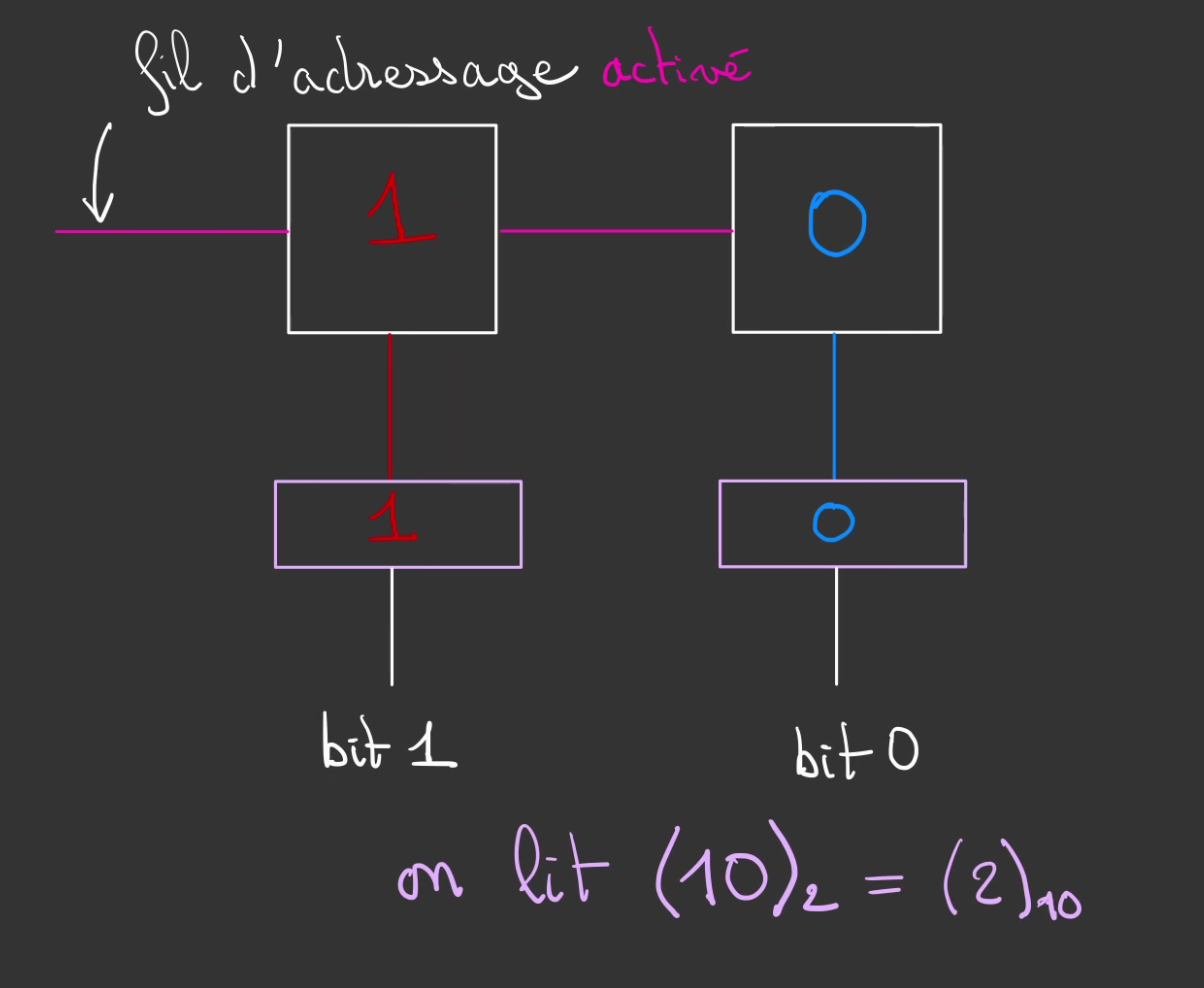

Ici nous allons représenter le nombre décimal 2 en mémoire. Pour cela on définit le bit 1 à 1 et le bit 0 à 0.

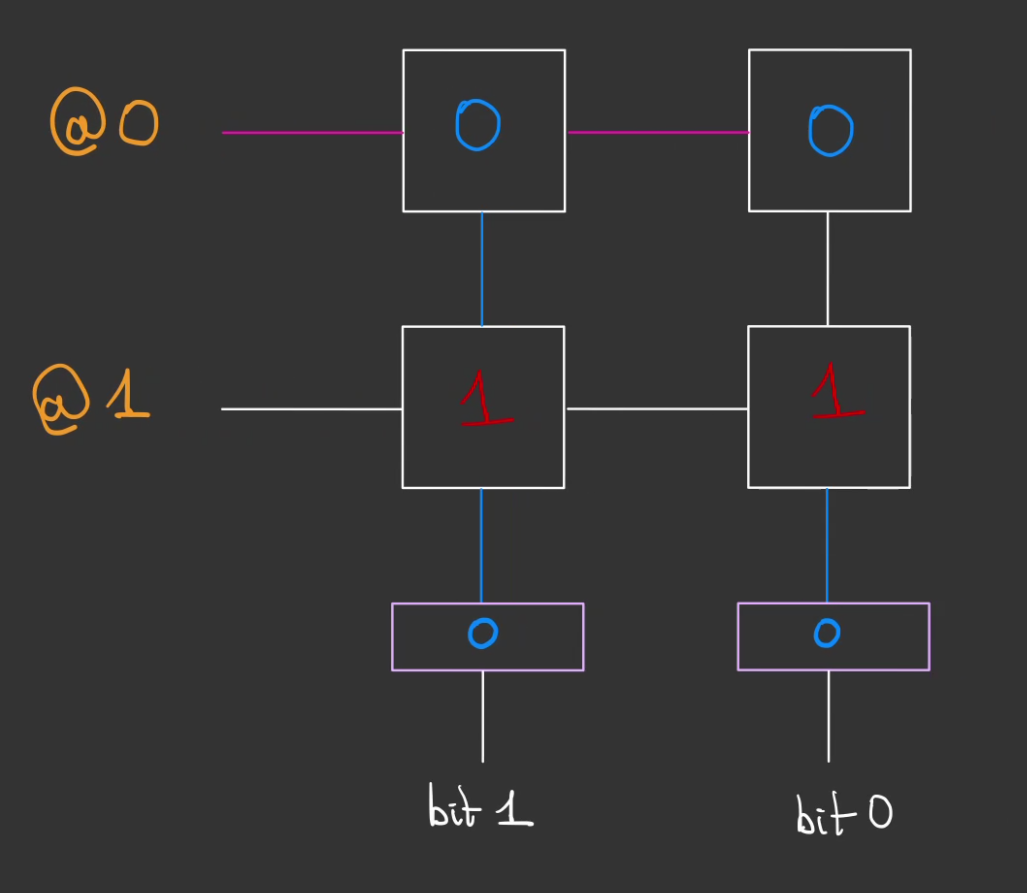

Si l'on veut lire les données stockées dans notre couple de cellule.

On active les deux cellules.

Ce qui permet de lire le mot binaire c'est à dire un ensemble de cellules ordonnées.

Ici ce mot vaut 10 en binaire ou 2 en décimale.

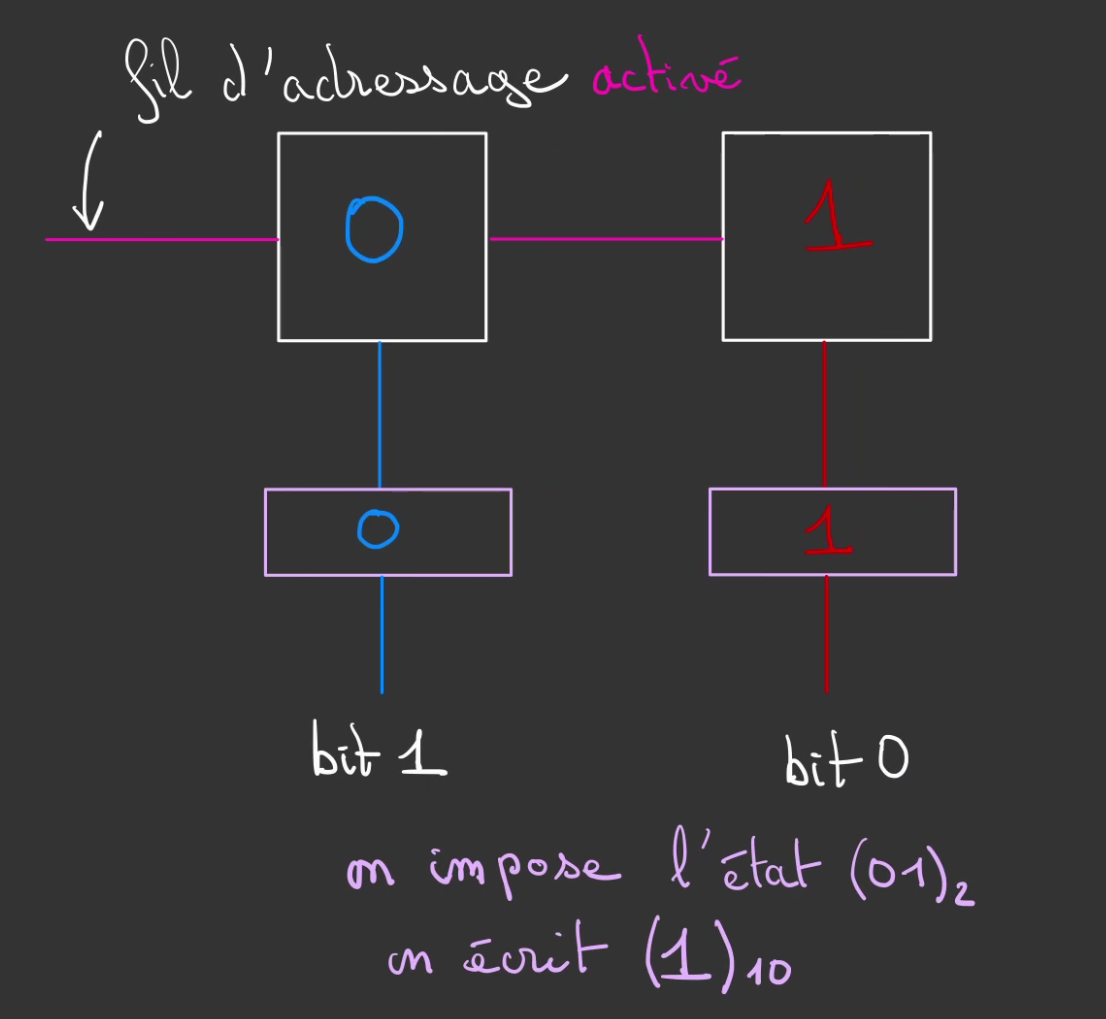

De la même manière si l'on désire enregistrer une valeur, mettons 01. On active le fil d'adressage. On applique la valeur respectivement voulue pour les cellules.

Ici :

- un 0 sur le bit1

- un 1 sur le bit0

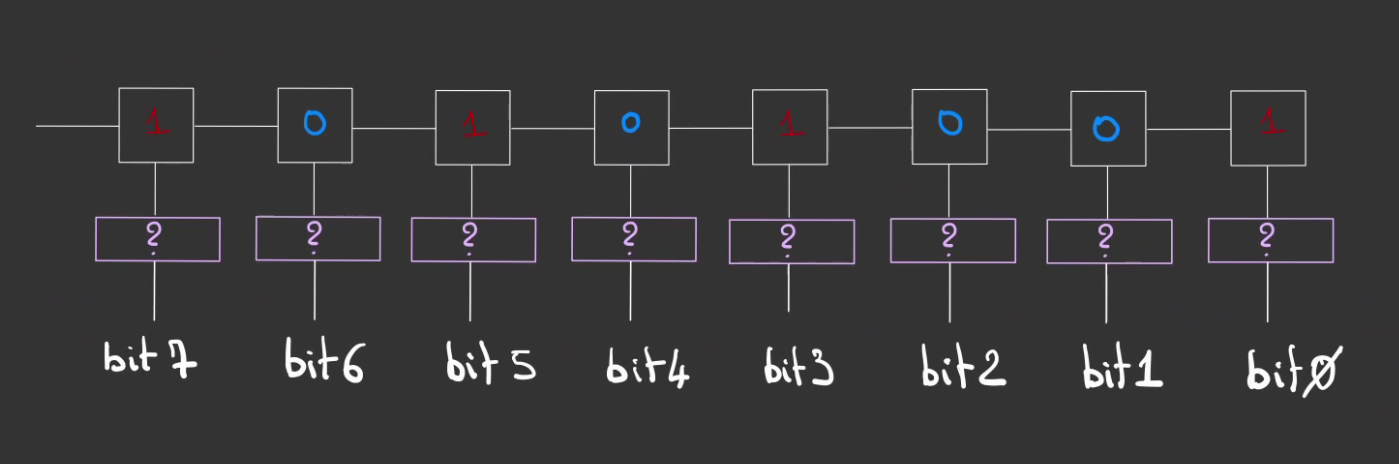

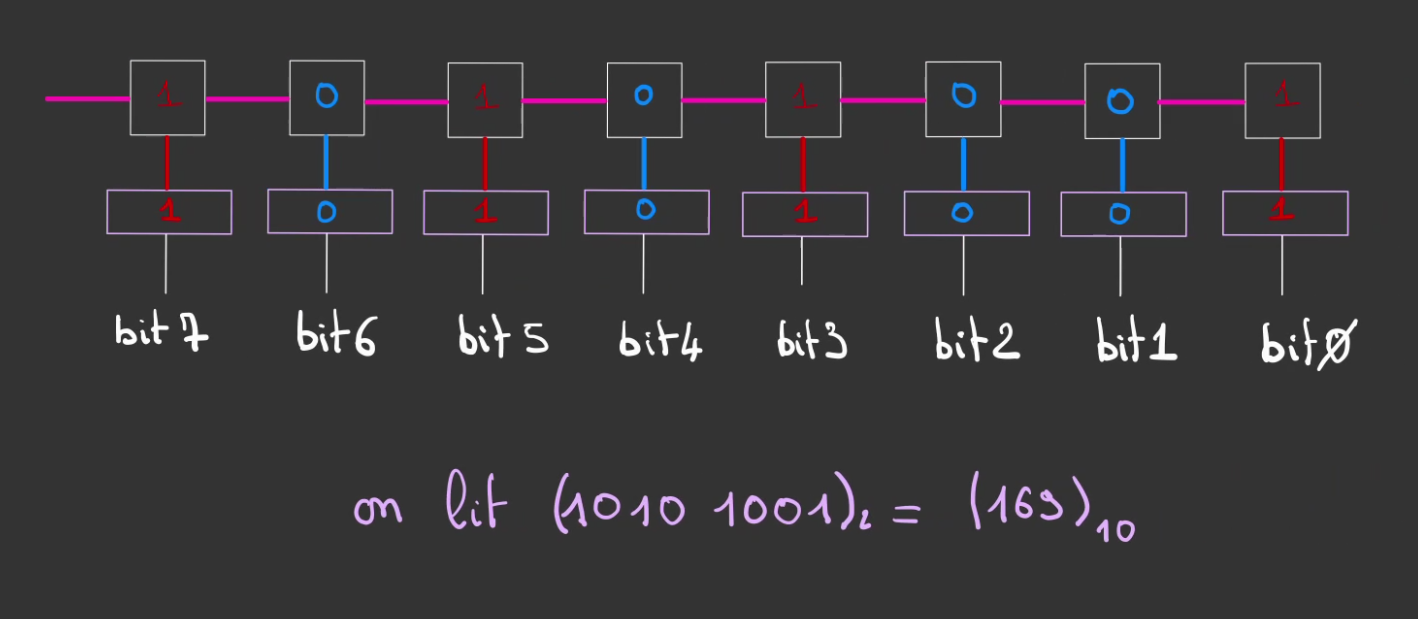

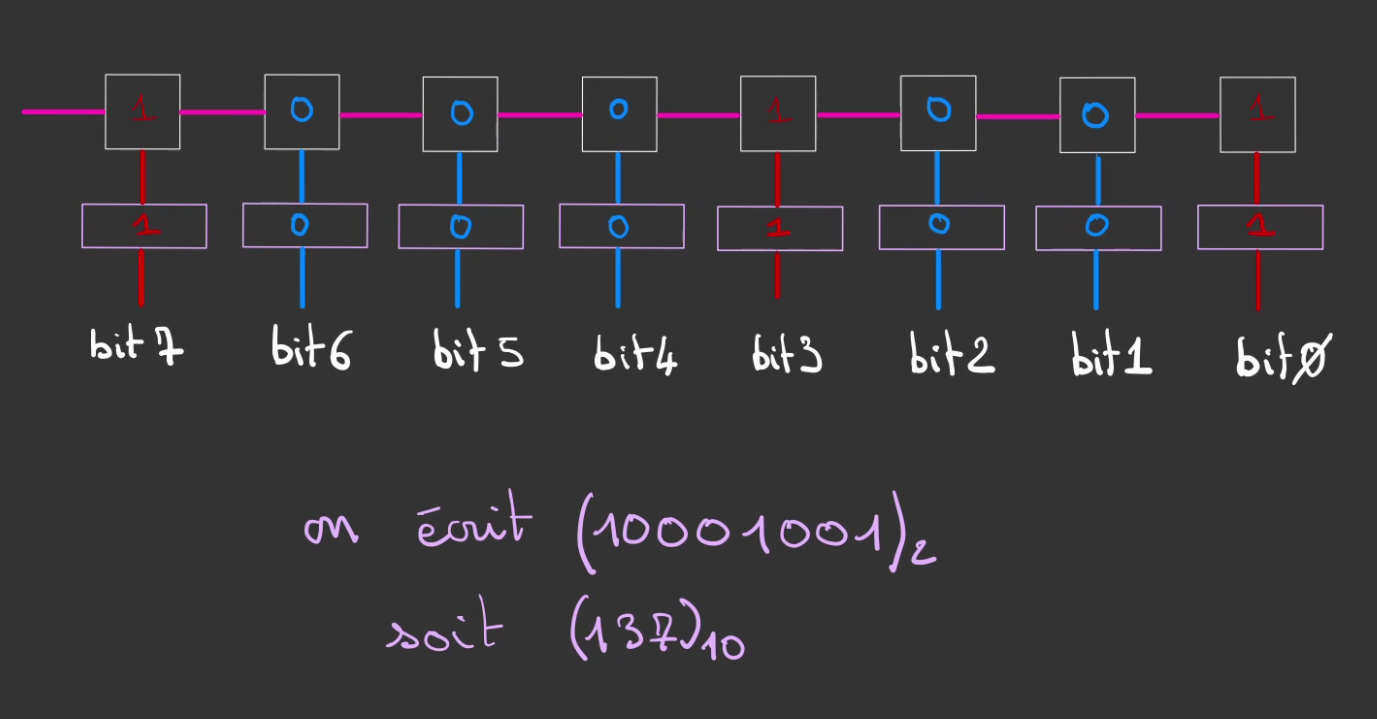

Pour stocker de plus grand nombre, on peut alors augmenter le nombre de cases qui constitue notre mot binaire, d'un mot de 2 bits, on passe à un mot de 8 bits.

Que l'on nomme plus communément un octet.

octet, signifie 8 pour "oct" comme dans octogone.

un ensemble de 8 bits.

Que l'on peut ainsi manipuler comme notre mot binaire de 2 bits.

En activant le fil d'adressage de la ligne du mot, on peut en lire sa valeur.

On peut alors également modifier le mot. En appliquant en entrée la valeur du mot voulu et en activant le fil d'adressage.

Et comme toujours, ce qui est vrai pour 1, 2, 8 est valable pour 1000. Faut juste beaucoup de fils. 🤣

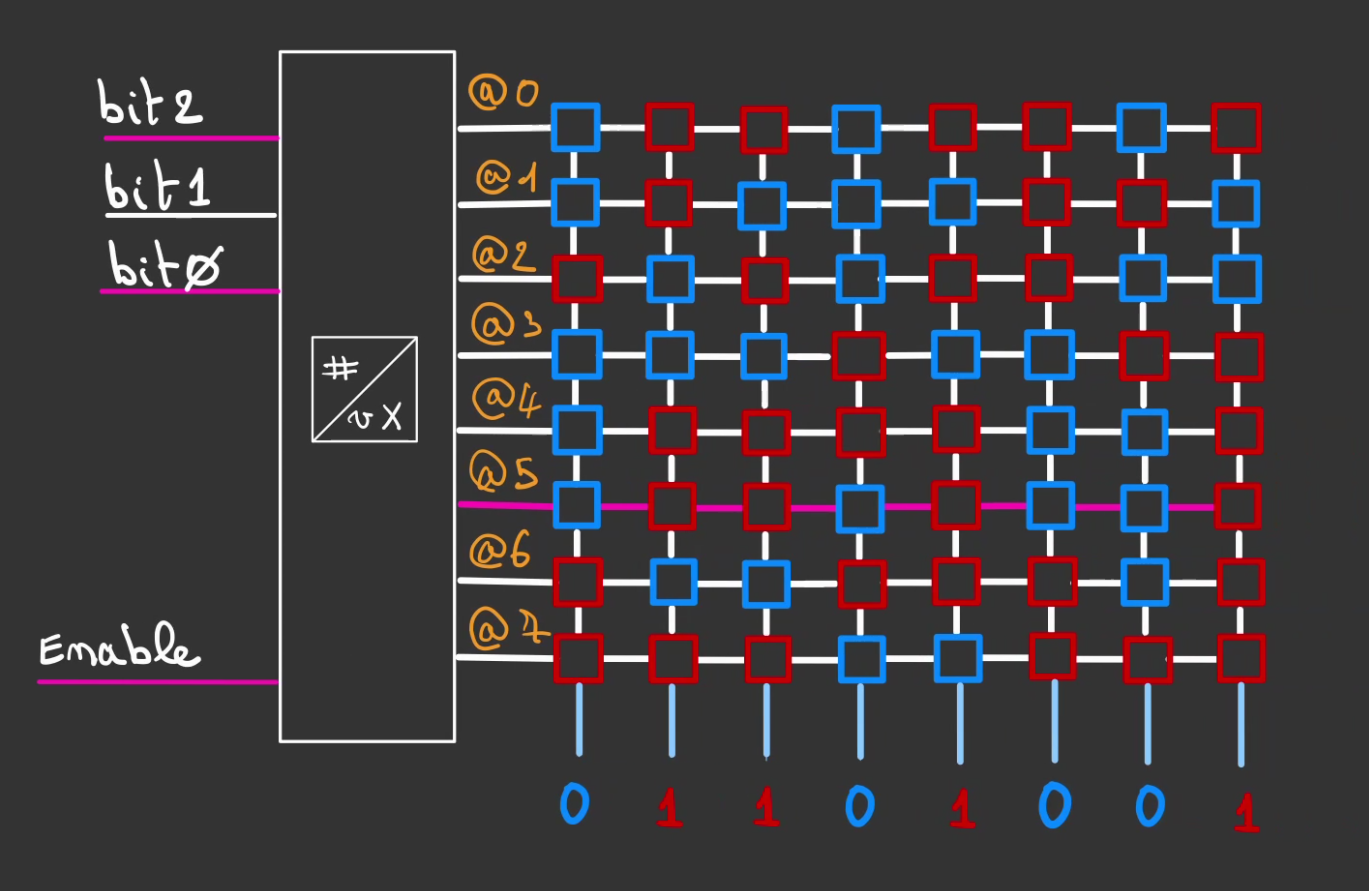

Matrice de mémoire

Bon! On peut stocker des nombres aussi grands que l'on veut, mais on ne peut en stocker qu'un seul. 😕

Il faut trouver un moyen d'en stocker déjà 2.

La solution est toute trouvée, nous allons les empiler.

Nous avons donc 2 mots différents.

Les lignes d'adressage sont communes aux mots et les colonnes de données sont communes aux bits des mots.

Pouvant de manière indépendante activer ou non une ligne d'adressage, on est dans la capacité de sélectionner le mot désiré.

Par exemple, ic, l'on désire modifier le mot à l'adresse @1.

On active la ligne correspondante et on applique la valeur.

Pour lire la valeur, c'est également la même chose.

On peut de manière indépendante sélectionner l'adresse @0. Et lire le mot qui y est contenu.

On a désormais un système complet qui permet de lire et écrire deux mots de 2 bits.

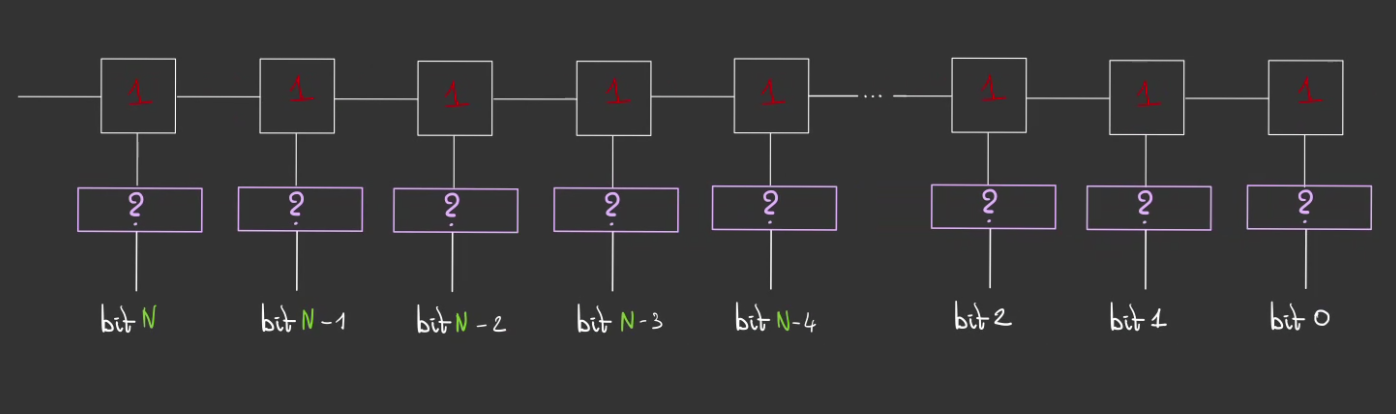

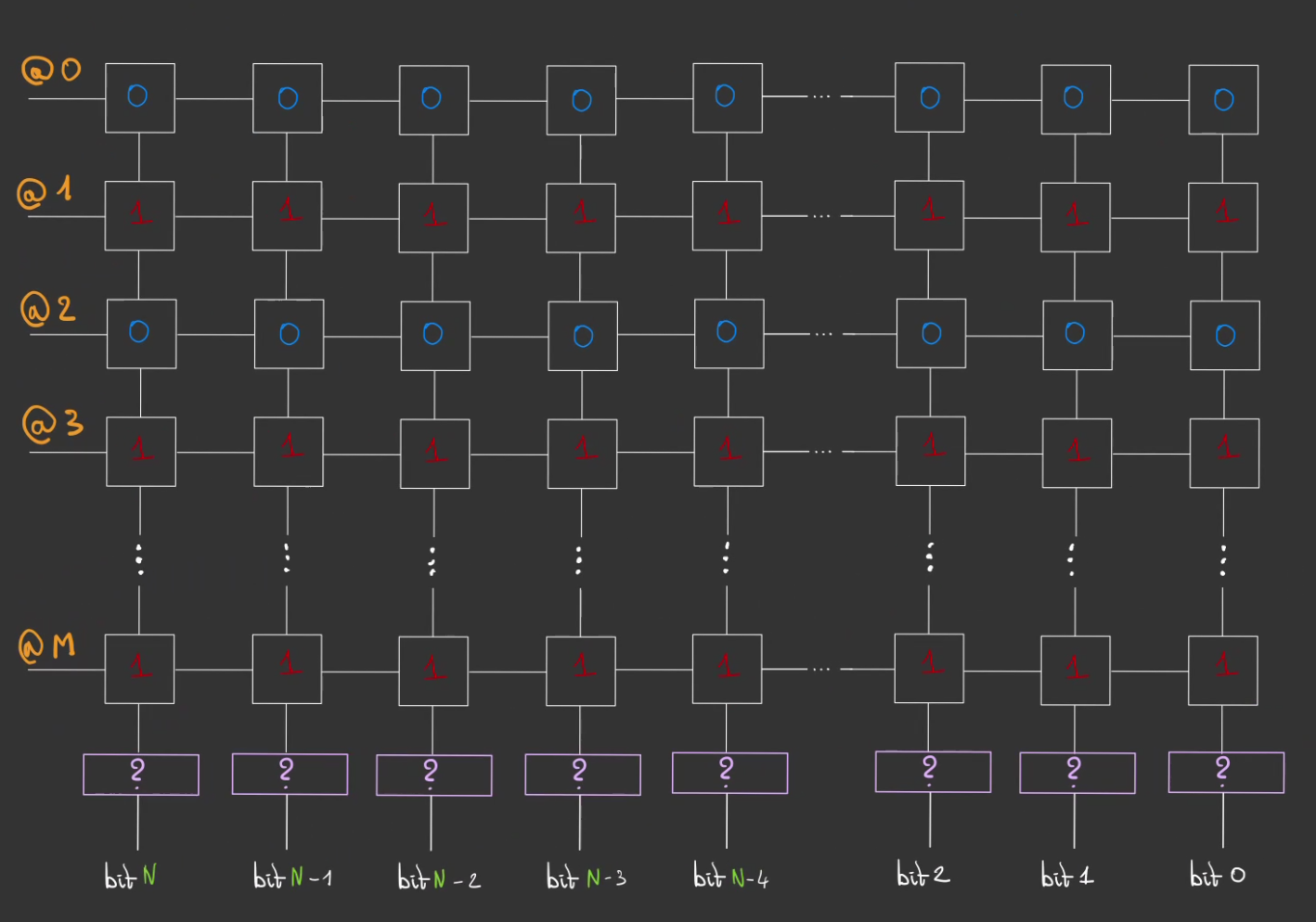

On peut alors généraliser !

On créé alors une matrice de M mots binaires de N bits.

Nous pouvons désormais, stocker la Terre entière et conquérir le monde !! 🌍

Adressage

Très bien, on a un joli système tout propre, capable de stocker de la donnée.

Pour le moment, j'ai passé sous silence ce souci.

Mais comment peut-on sélectionner la ligne que l'on désire ?

Surtout lorsqu'on a plus de deux mots.

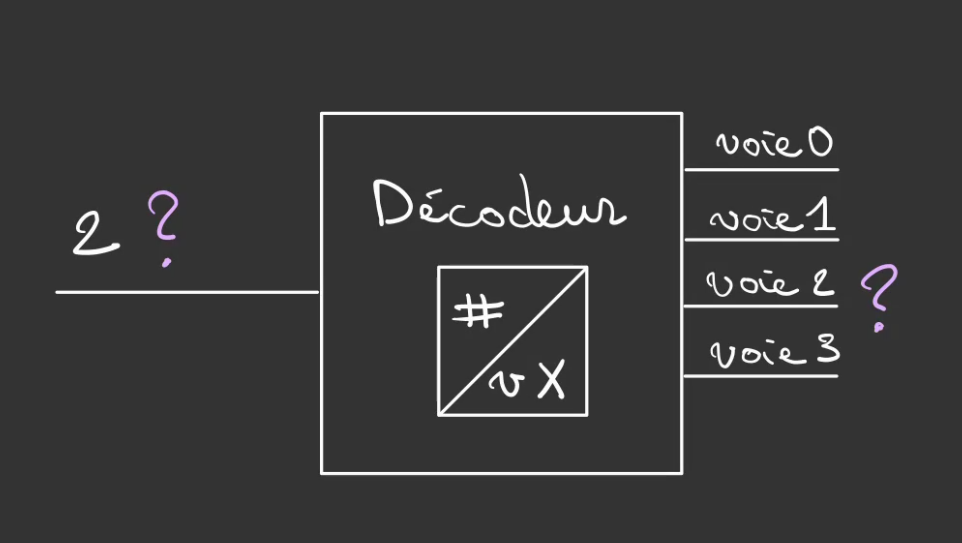

Decodeur

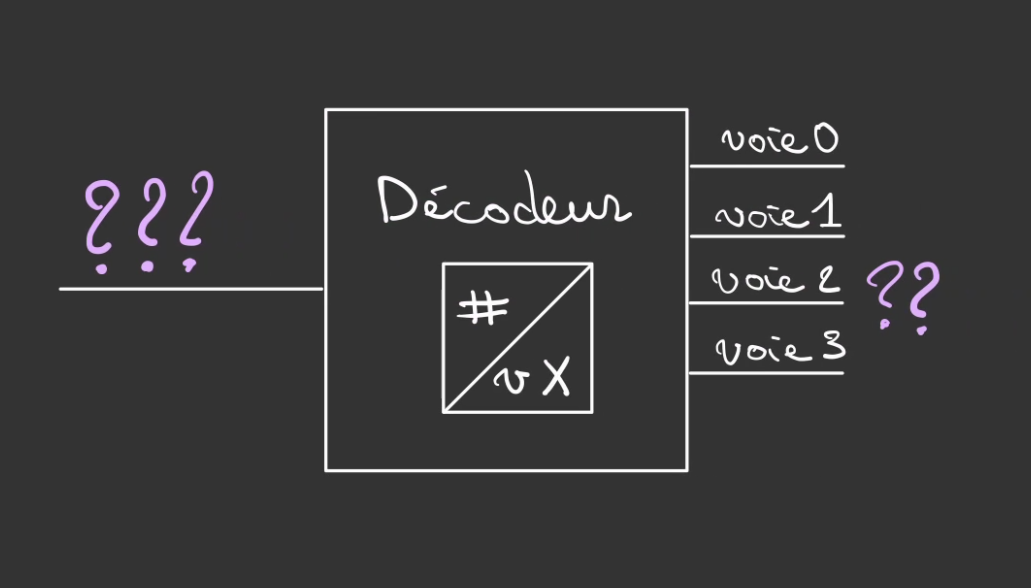

C'est alors qu'intervient un système qui se nomme un décodeur.

Il s'agit d'une sorte de gare de routage.

On lui dit quelle voie doit être activée et lui active la voie correspondante.

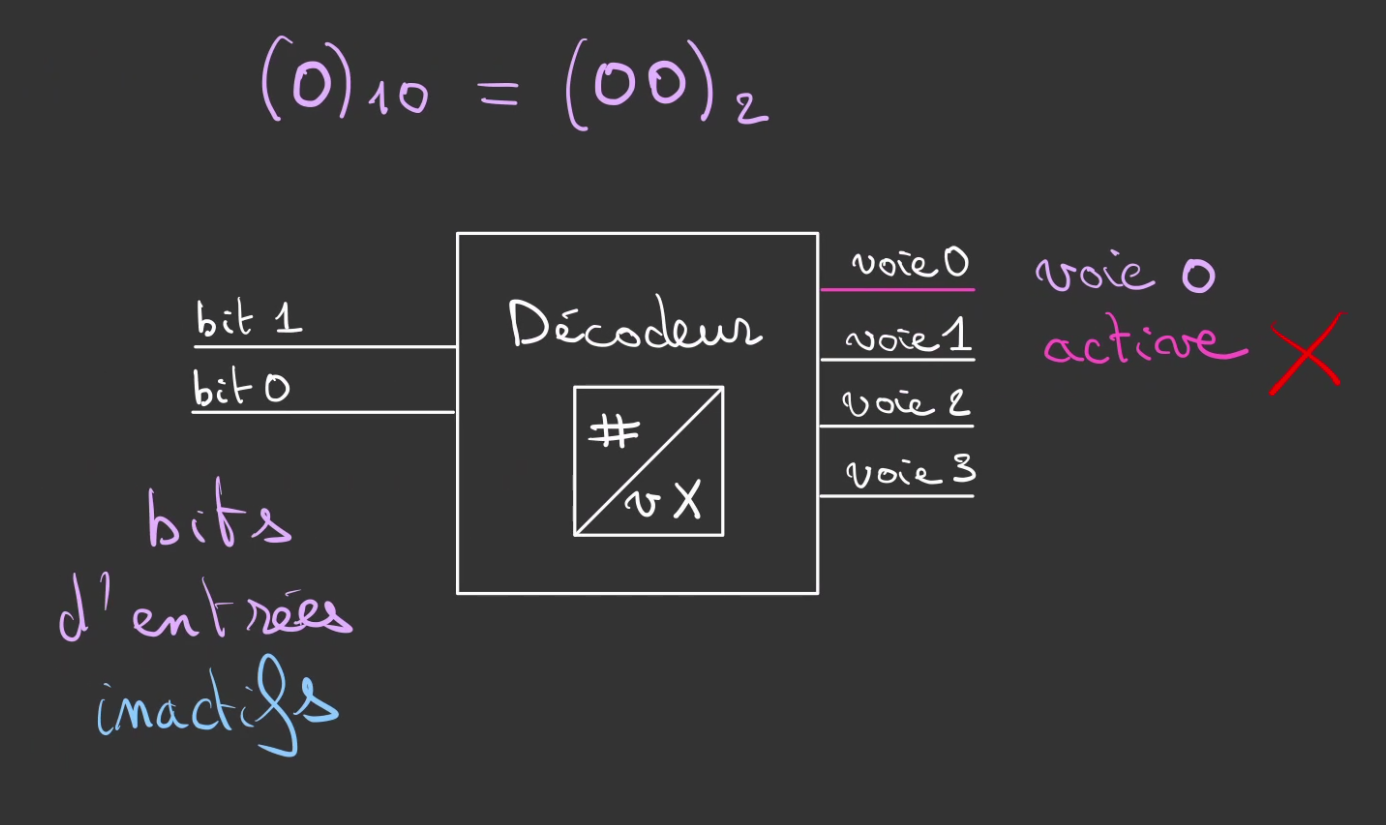

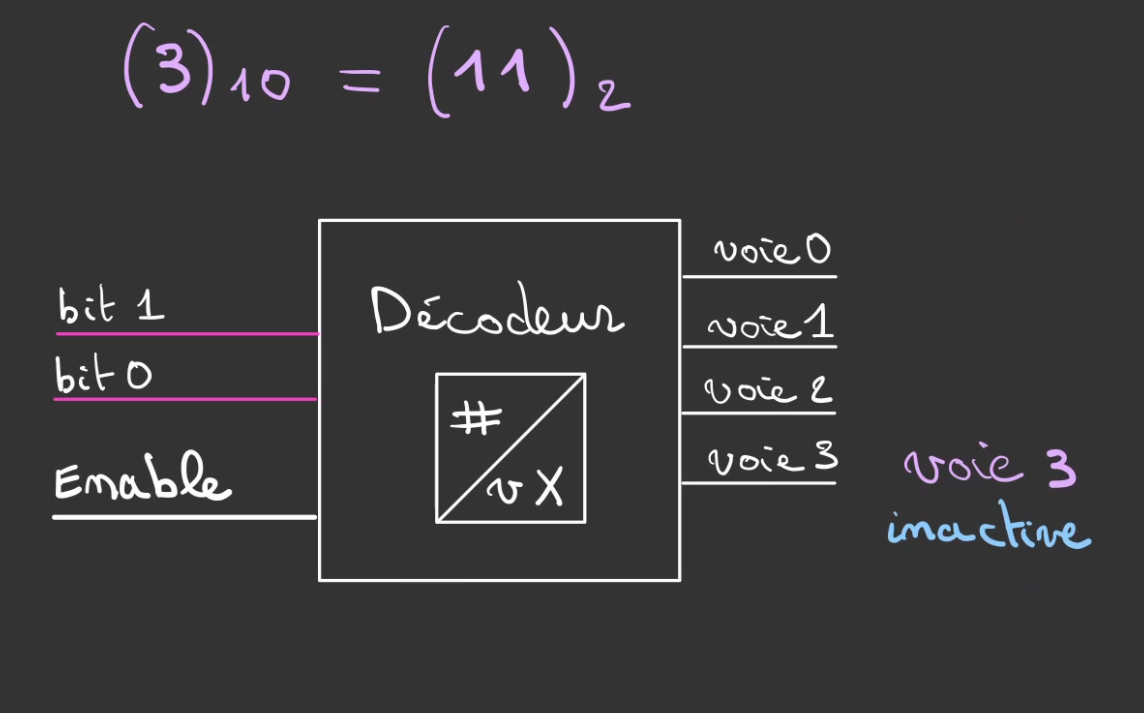

Prenons un exemple avec 4 voies.

Comment pouvons nous piloter l'entrée de gauche pour que la voie2 soit la seule activée ?

Mettons que l'on veille définir directement la sortie par son numéro.

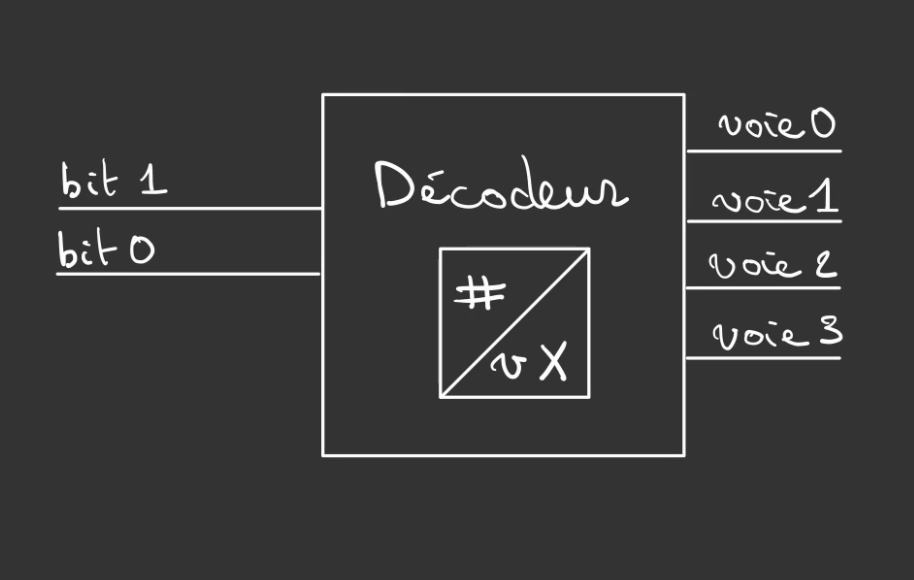

Et bien on va encoder ce nombre avec des fils.

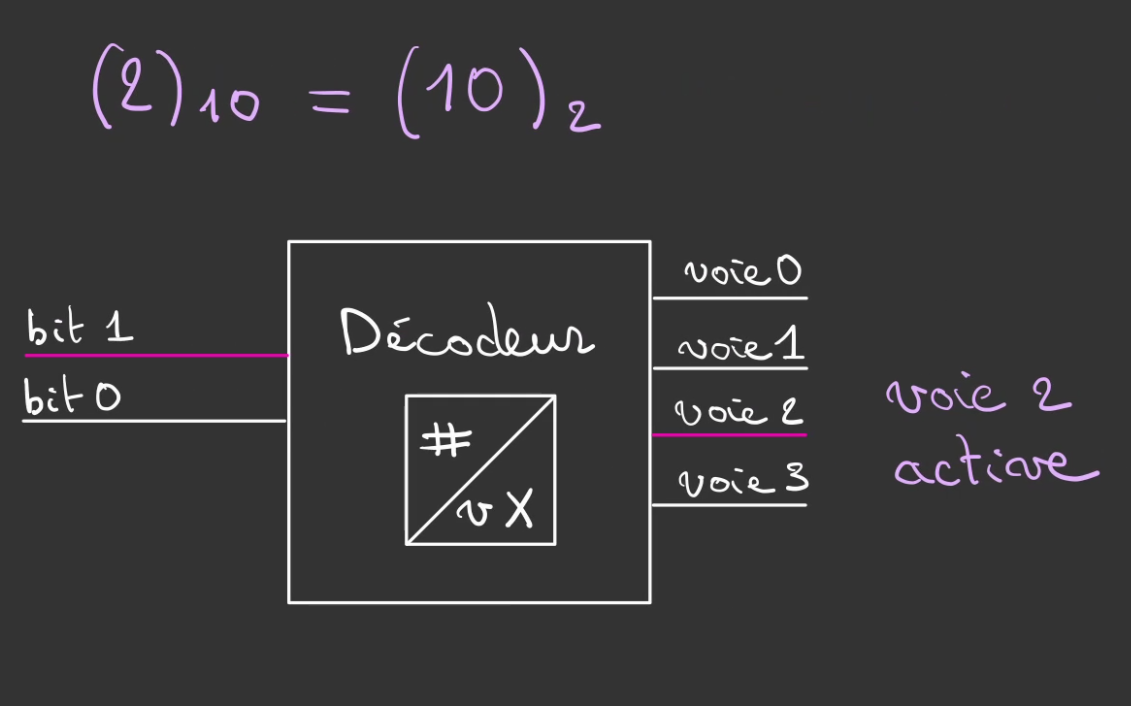

On définit binairement ce 2.

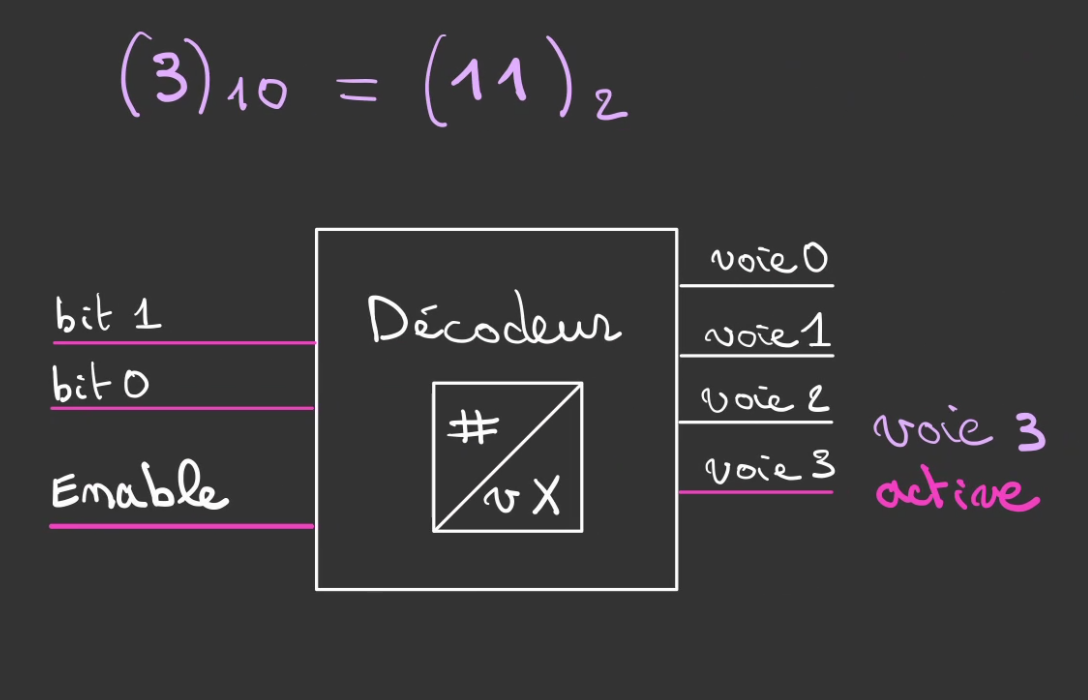

De cette manière, on vient sélectionner la voie que l'on désire.

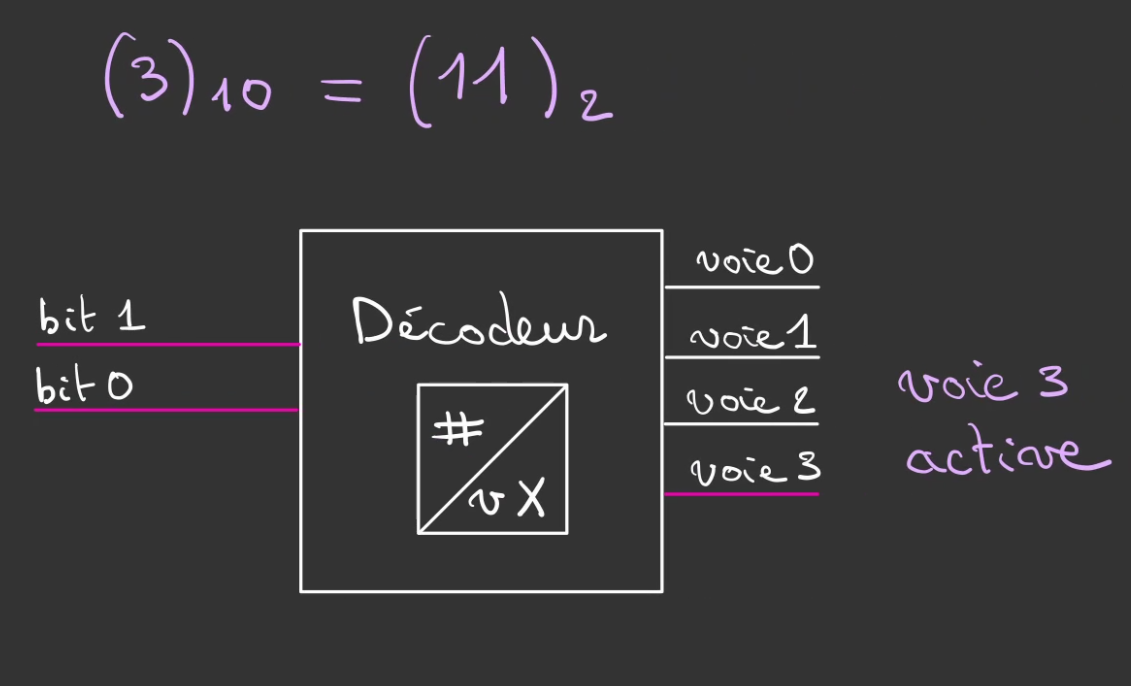

On peut alors le faire pour toutes les voies, ici un 3.

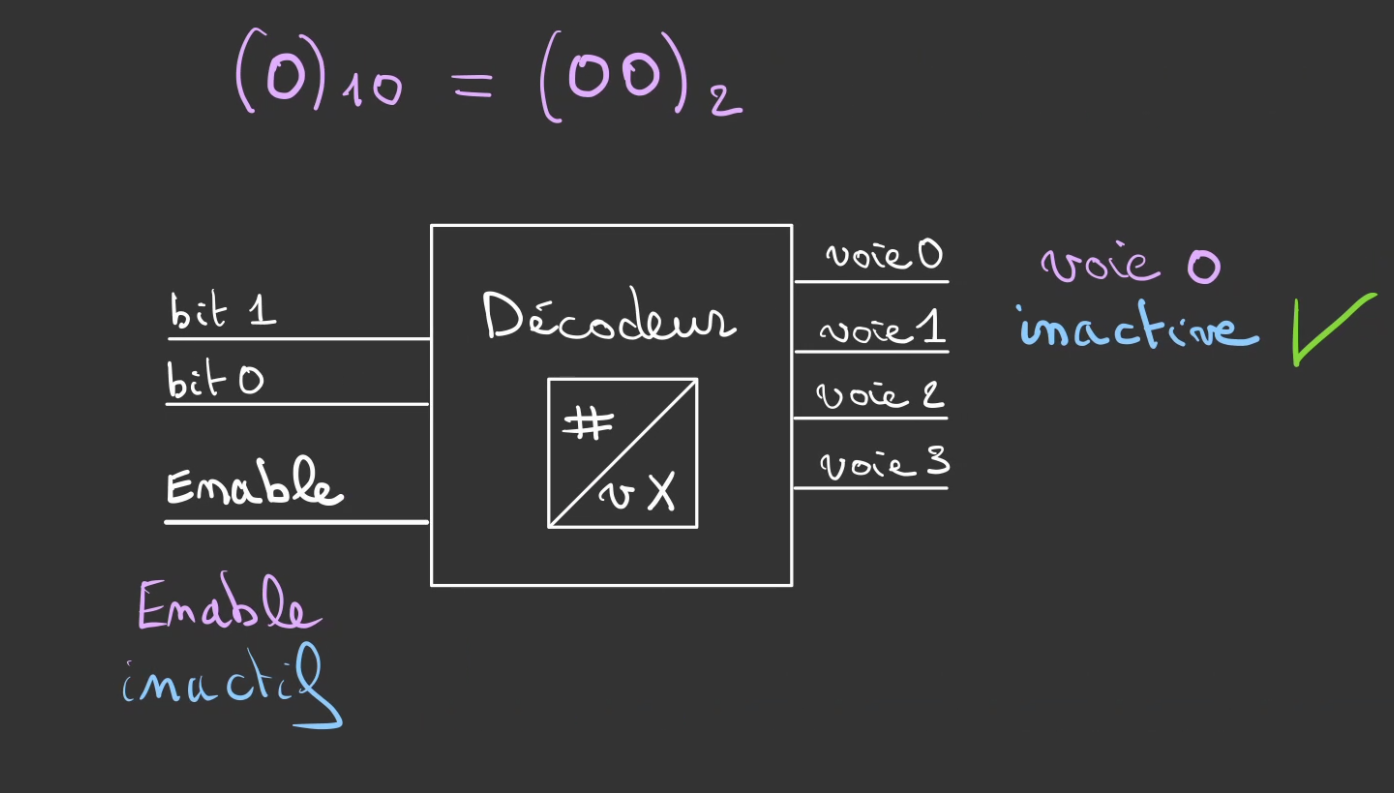

Par contre on a un souci, même quand on ne veut rien sélectionner, la voie 0, reste active.

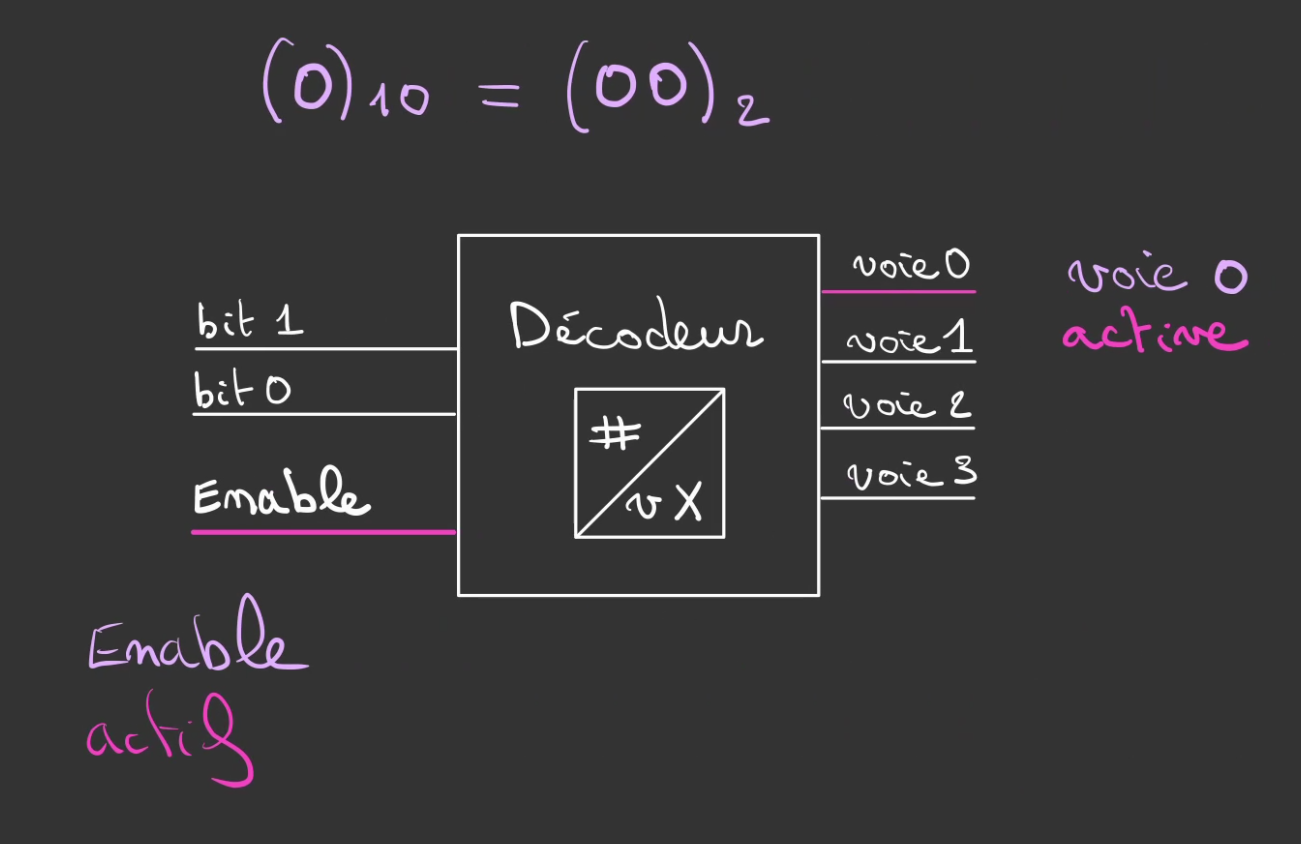

On ajoute alors un troisième fil Enable qui permet de contrôler la sortie du décodeur:

- si état bas, aucune voie n'est allumée

- si état haut, la voie sélectionnée est allumée

On peut alors contrôler ce que l'on désire comme voie en maintenant un état haut sur Enable.

Ou inhiber la sortie même si les bits d'entrées sont actifs

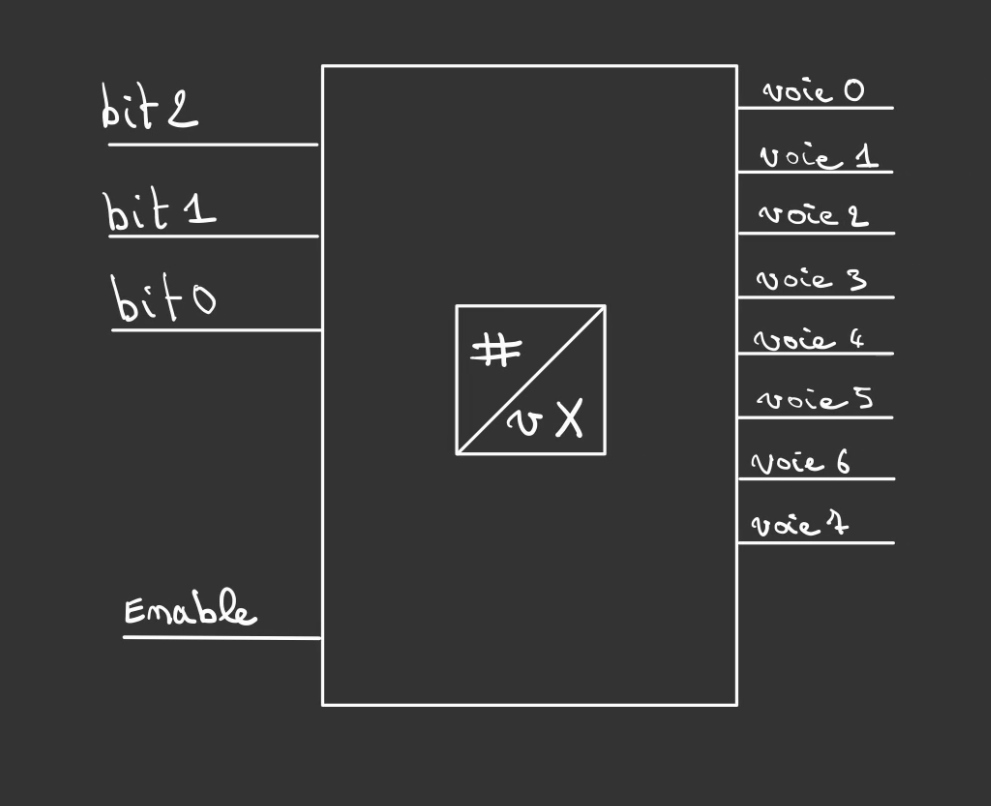

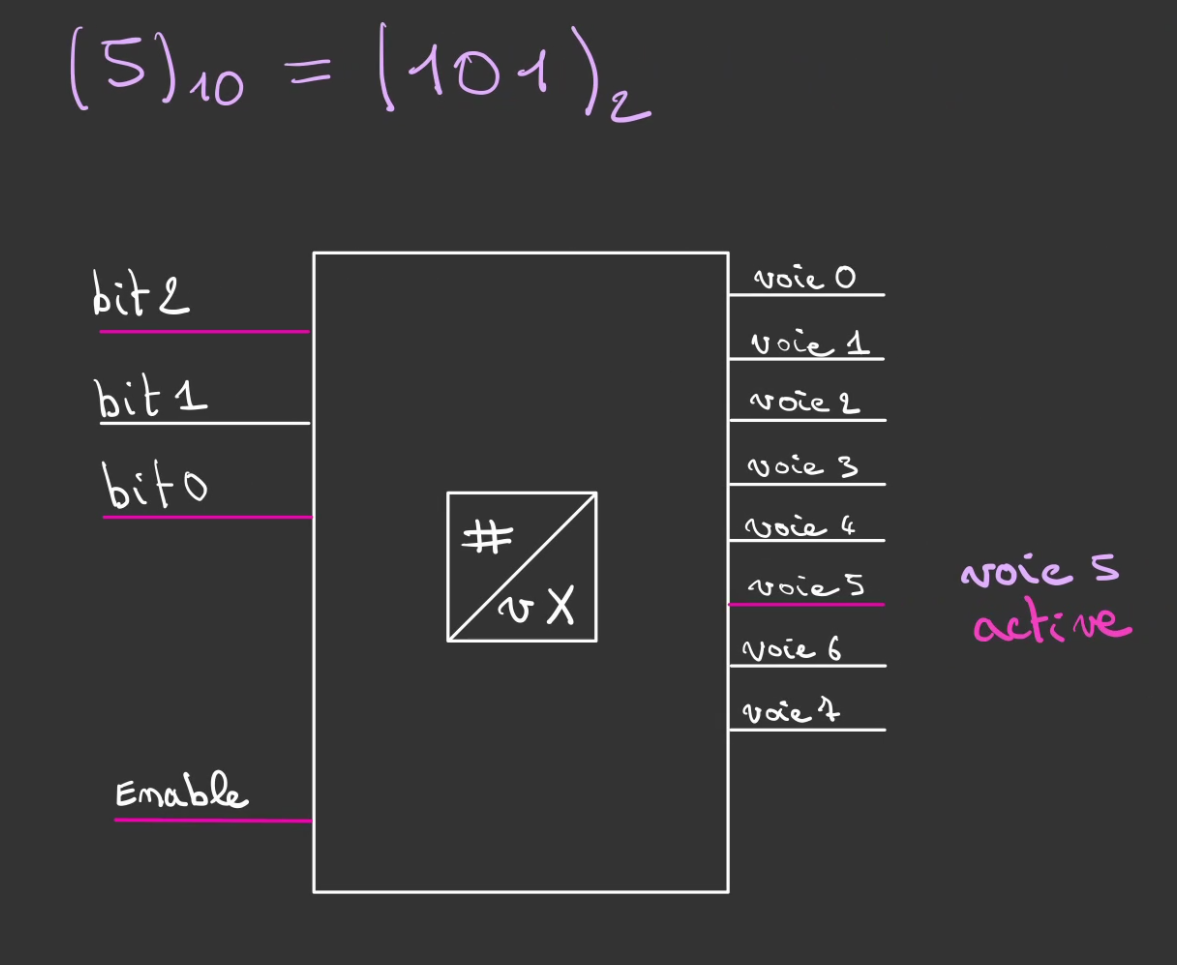

Si l'on a besoin de plus de voies que 4, il nous faut un fil d'entrées supplémentaire.

Car 2^3 = 8

Celui-ci se contrôle de la même manière.

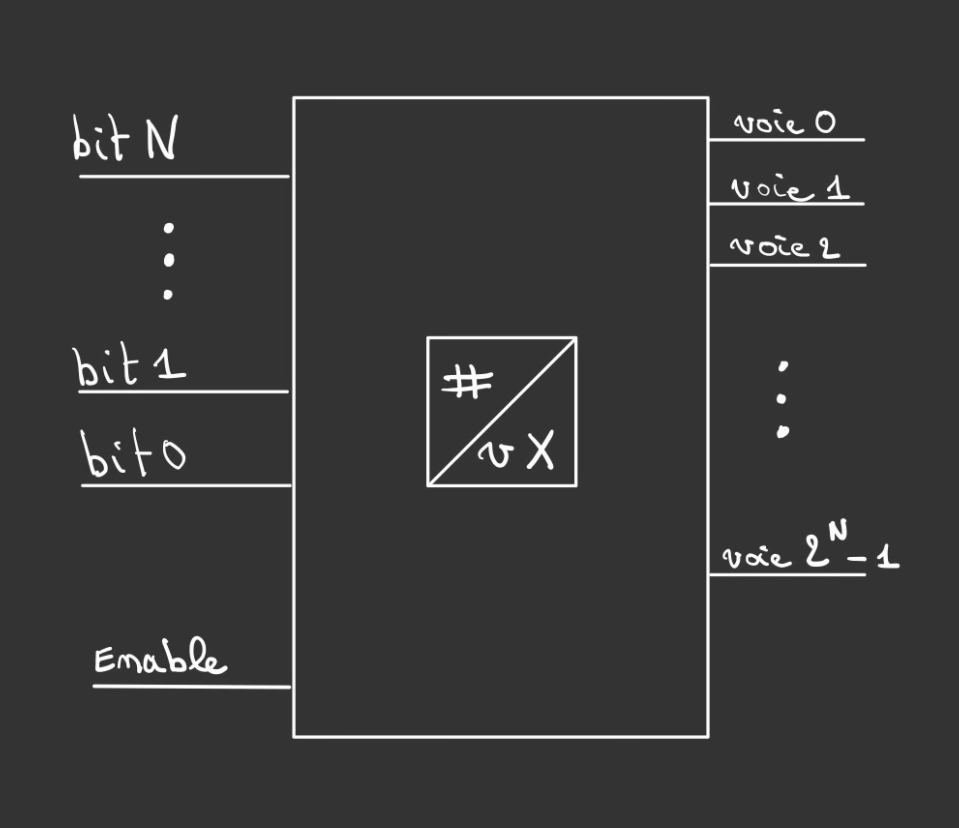

On peut alors généraliser.

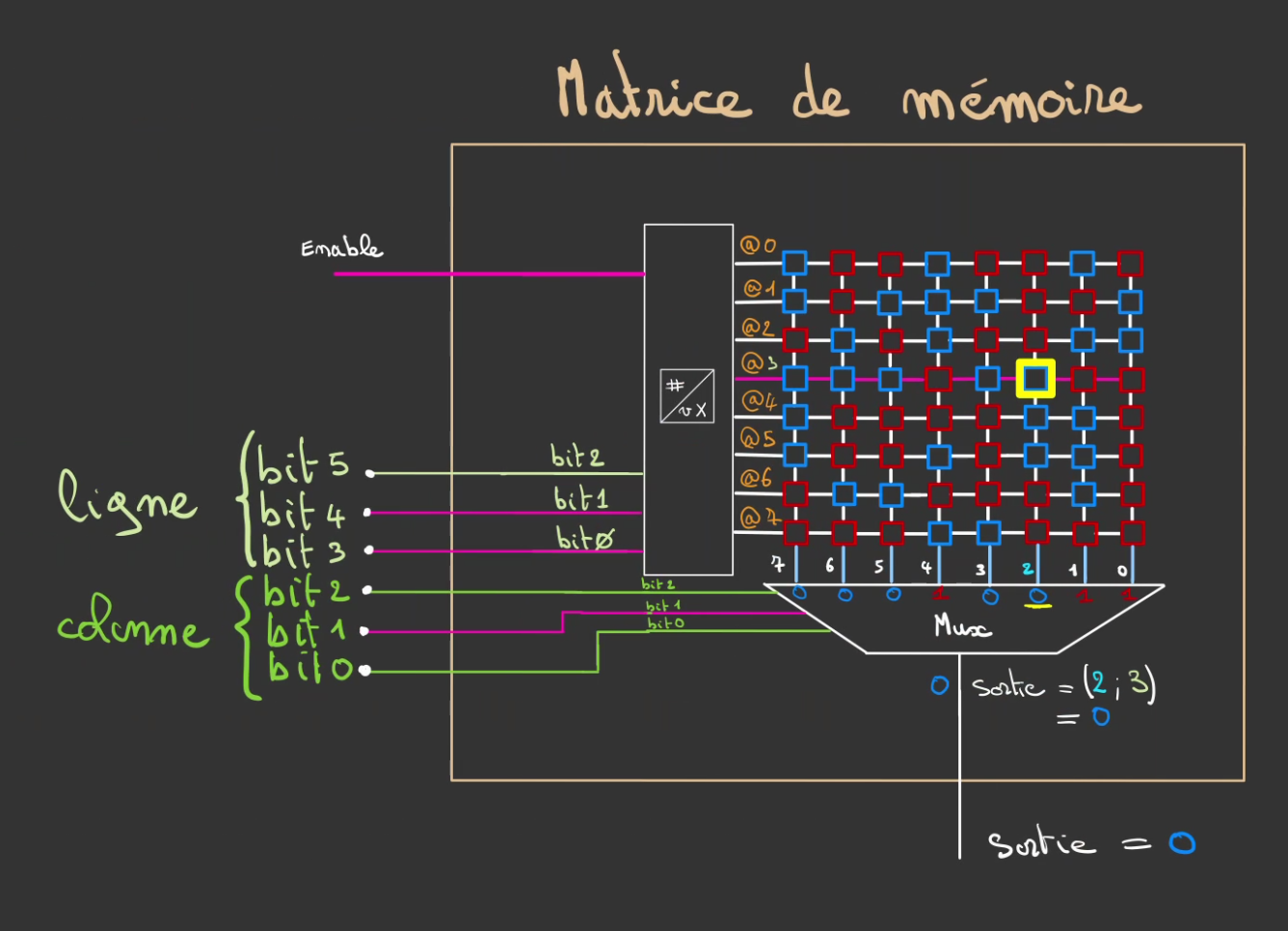

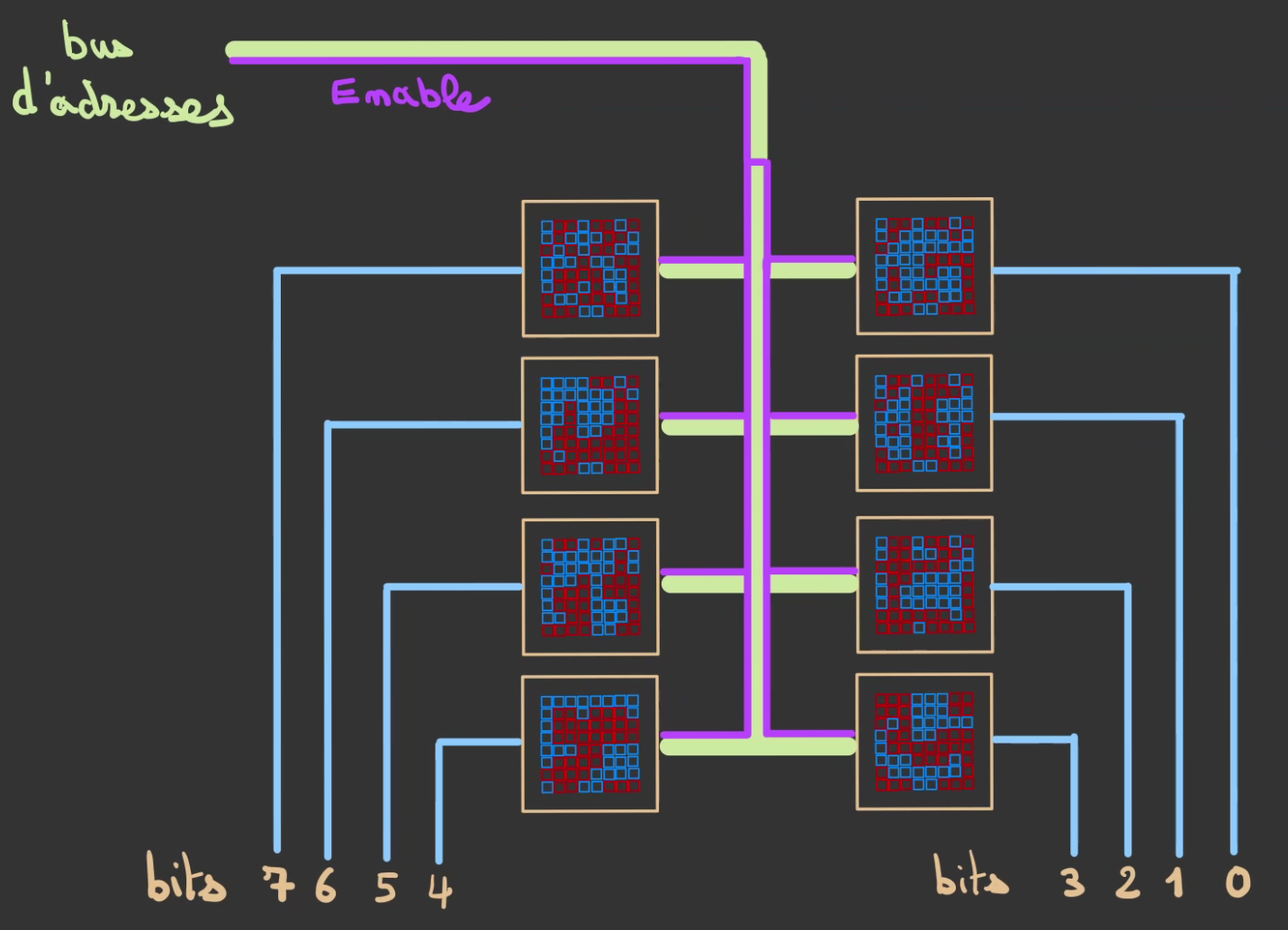

Selection de la ligne

On a donc un système qui nous permet de sélectionner une ligne parmi un ensemble d'autres.

On va donc coler un décodeur sur notre matrice de mémoire.

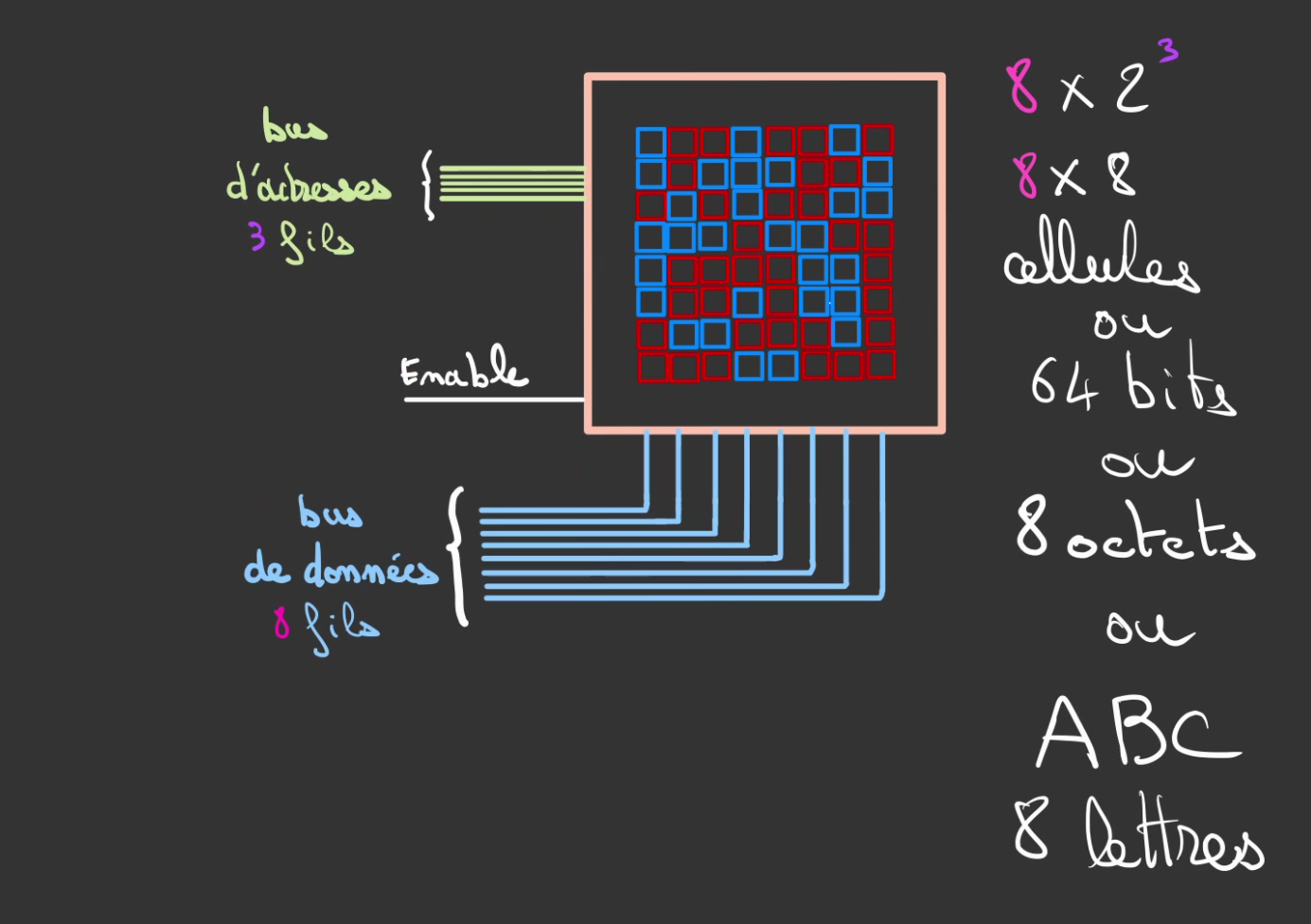

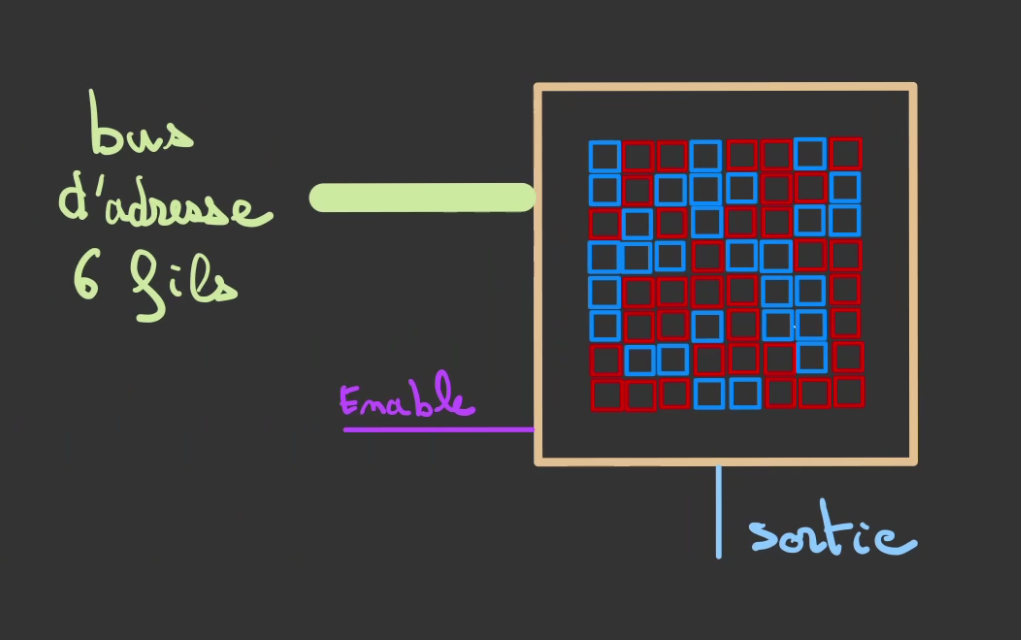

On peut alors en faire une jolie boîte.

On peut alors, sortir 3 fils qui constitueront notre bus d'adresses. Ici de 3 bits.

Et un bus de données de 8 bits.

Avec supplément un signal d'activation de la boîte. Qui correspond au Enable de notre décodeur.

Ce qui permet de pouvoir stocker un mot de 8 lettres.

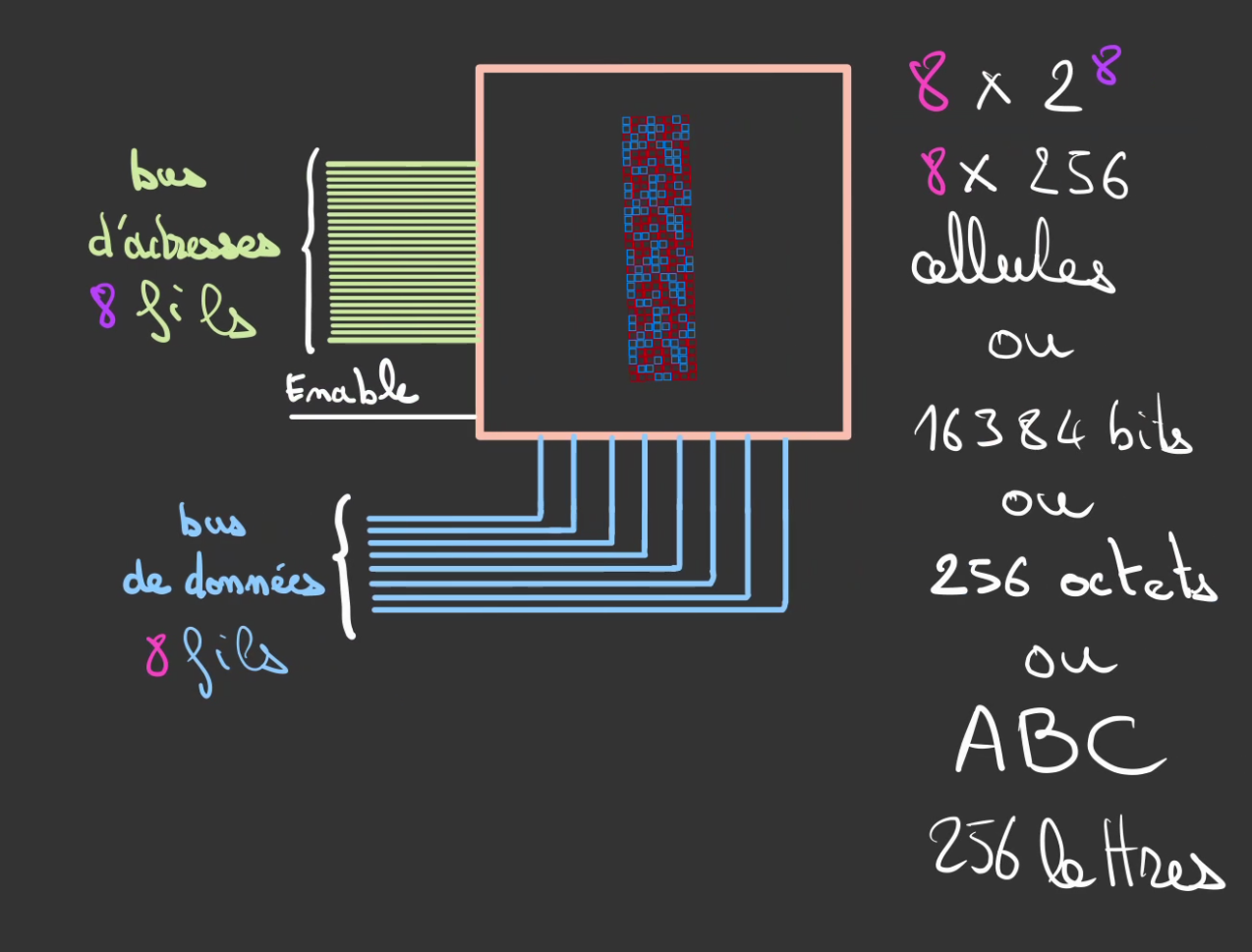

On peut alors augmenter le nombre de fils d'adresse pour venir faire grandir en hauteur la matrice.

Ici, on passe à 8 bits d'adresses et donc 256 lignes possibles.

On augmente alors d'autant la quantité de données stockable à une valeur incroyable de 256 octets.

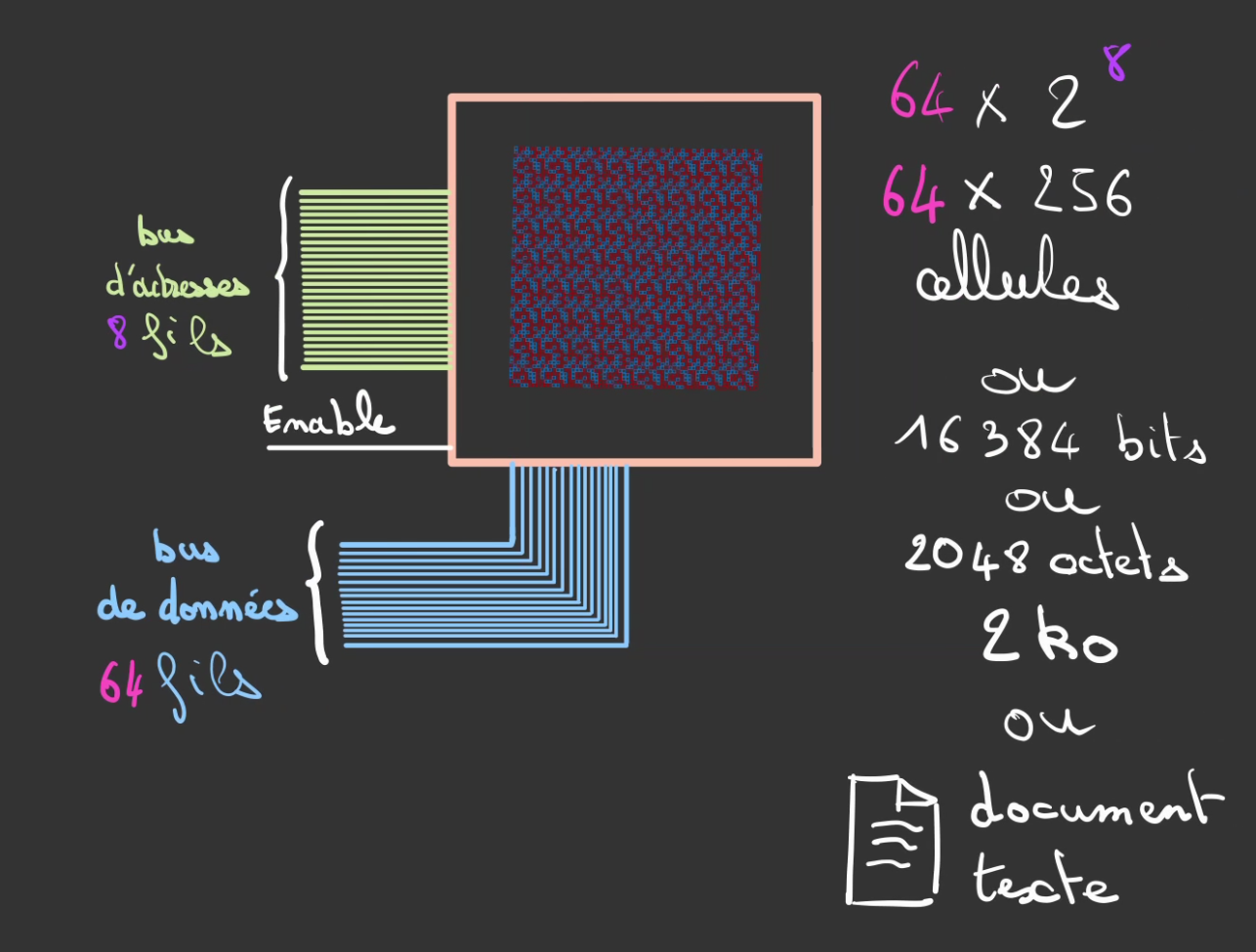

On peut également augmenter la largeur du bus de données pour lui faire atteindre les 64 fils.

Mais on reste ridicule en termes de stockage. 2 kilo-octets soit un fichier.

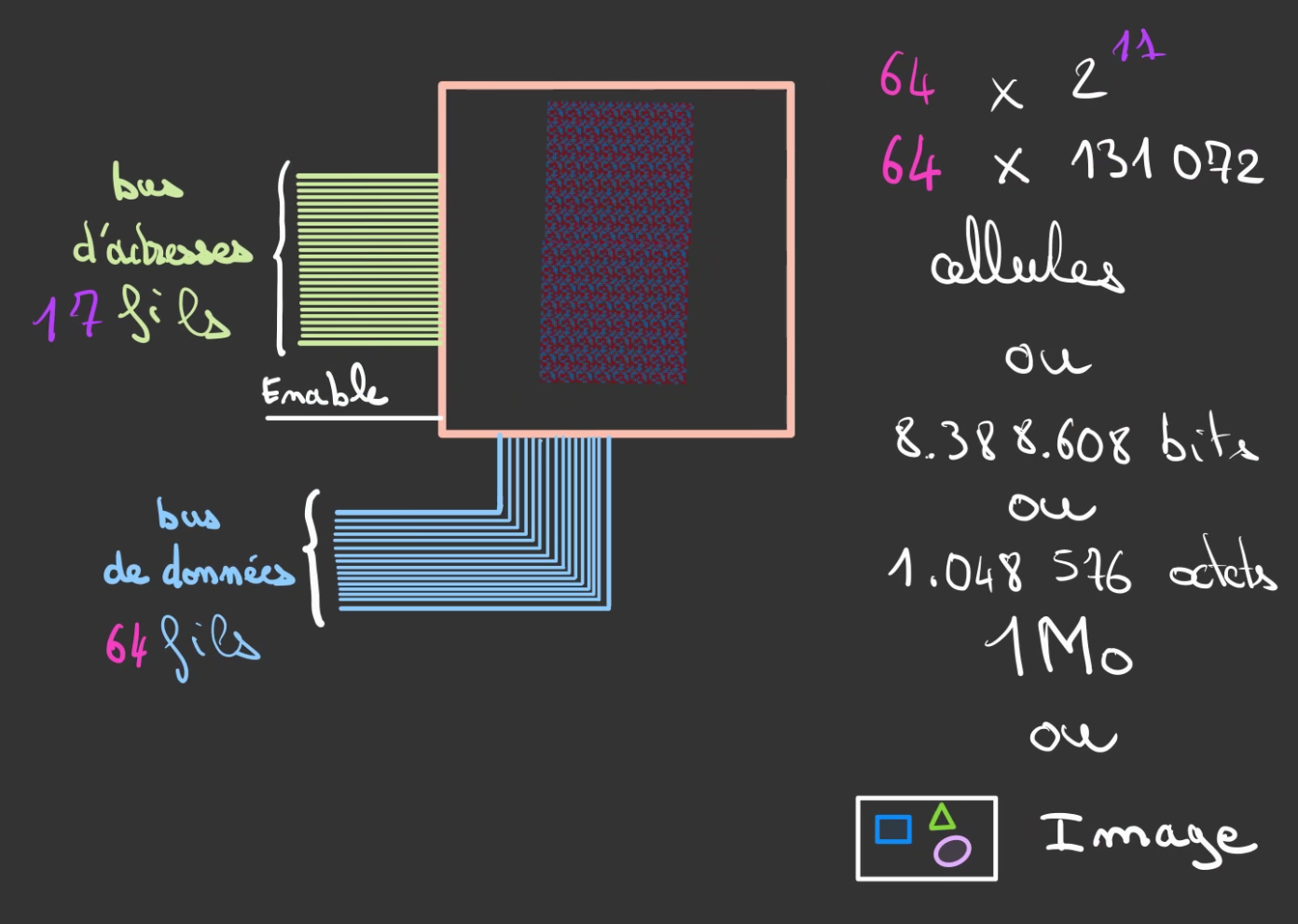

Si on augmente à 17 fils le bus de d'adresse.

On atteint péniblement les 1 méga-octet, une pauvre image. 😫

On pourrait augmenter le nombre de fils du bus de données, mais celui-ci ne peut pas grandir excessivement.

Je crois l'on ne va pas y arriver comme ça ...

Il nous faut un autre angle.

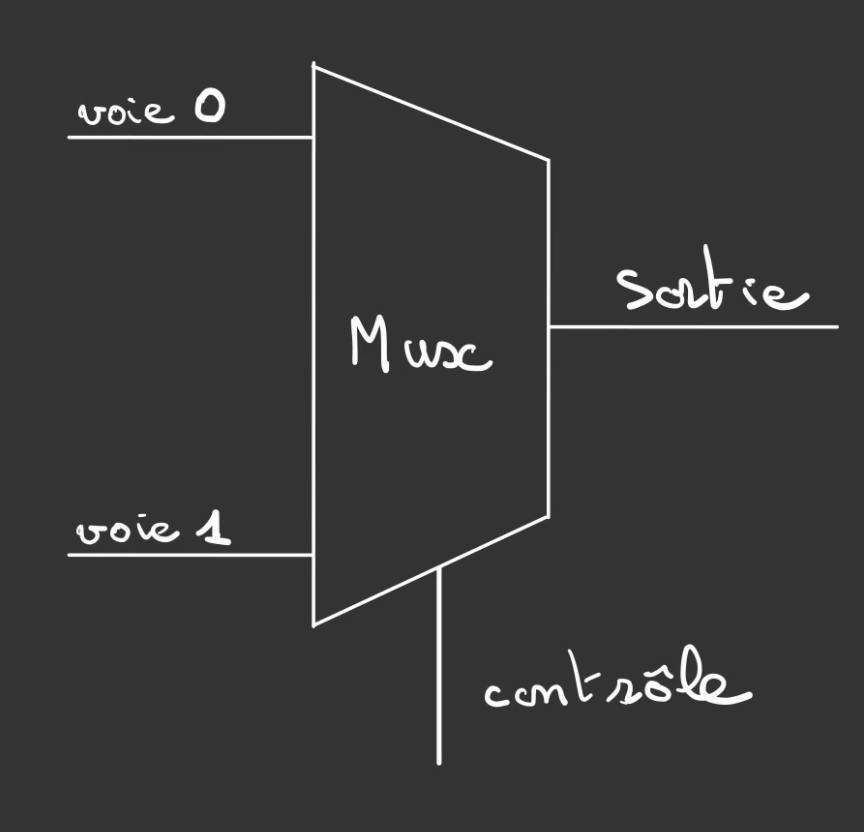

Multiplexeur

Avant de continuer notre chemin vers de plus grande valeur de stockage.

Nous allons faire un tour sur un autre système.

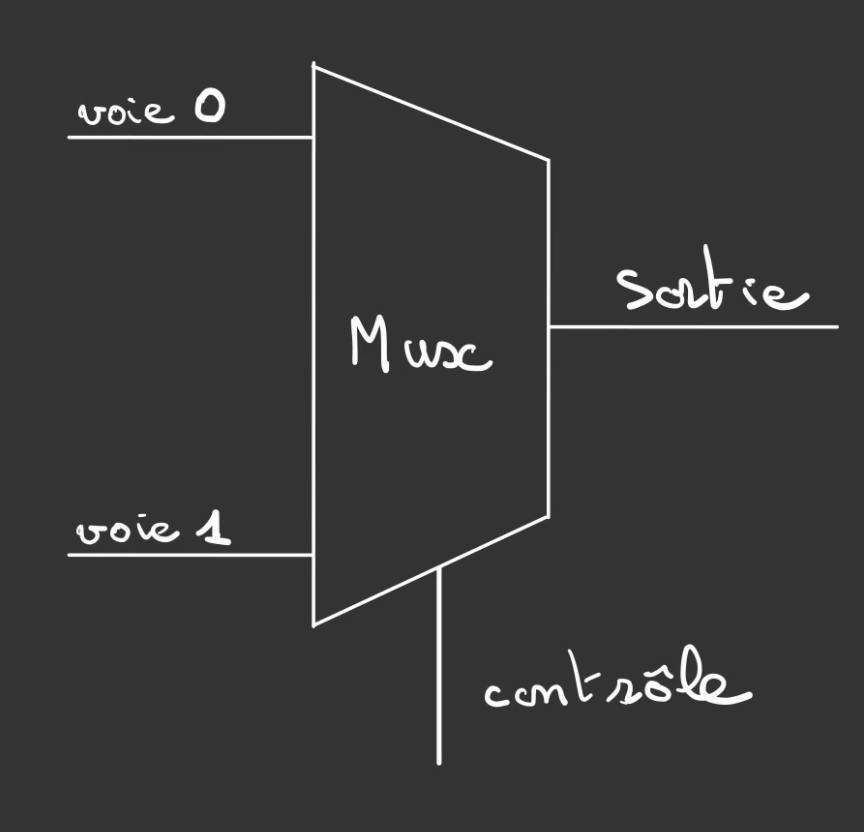

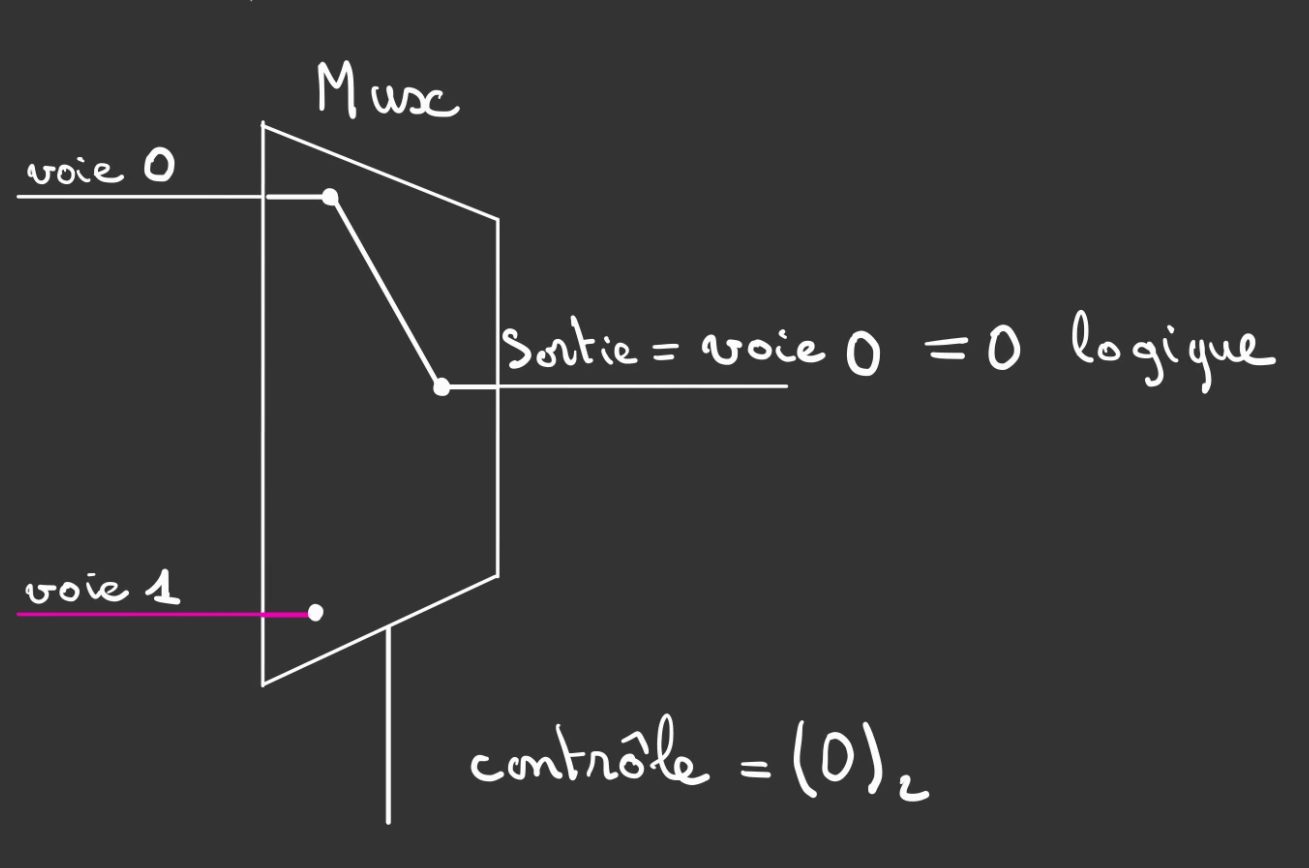

Celui-ci possède deux entrées appelées voie 0 et voie 1.

L'idée du composant est de venir connecter l'une des voies à la sortie selon le signal de contrôle.

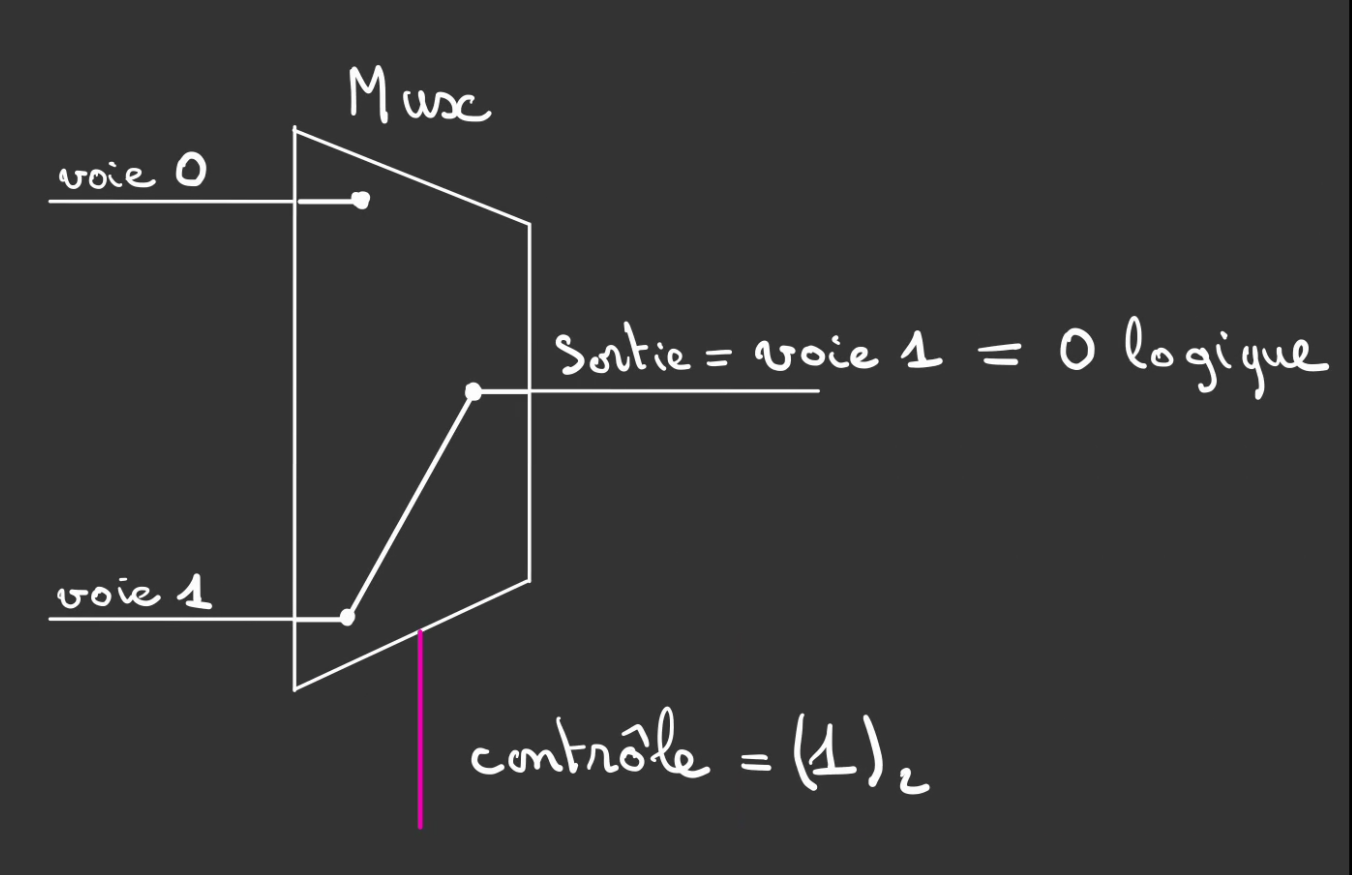

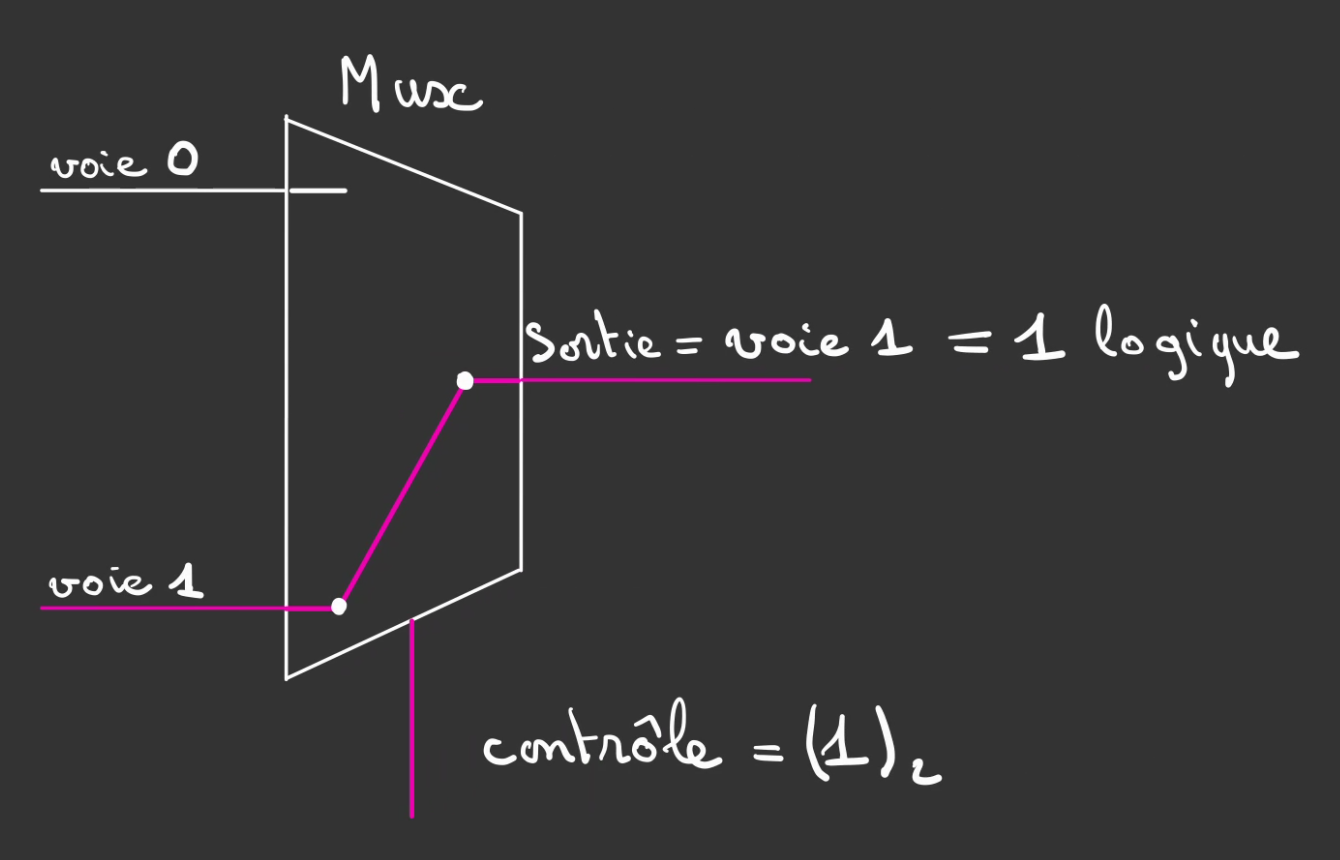

Si le signal de contrôle est à 1, alors on connecte la voie 1 à la sortie.

Ici, le signal de la voie 1 vaut 0 donc la Sortie vaut également 0.

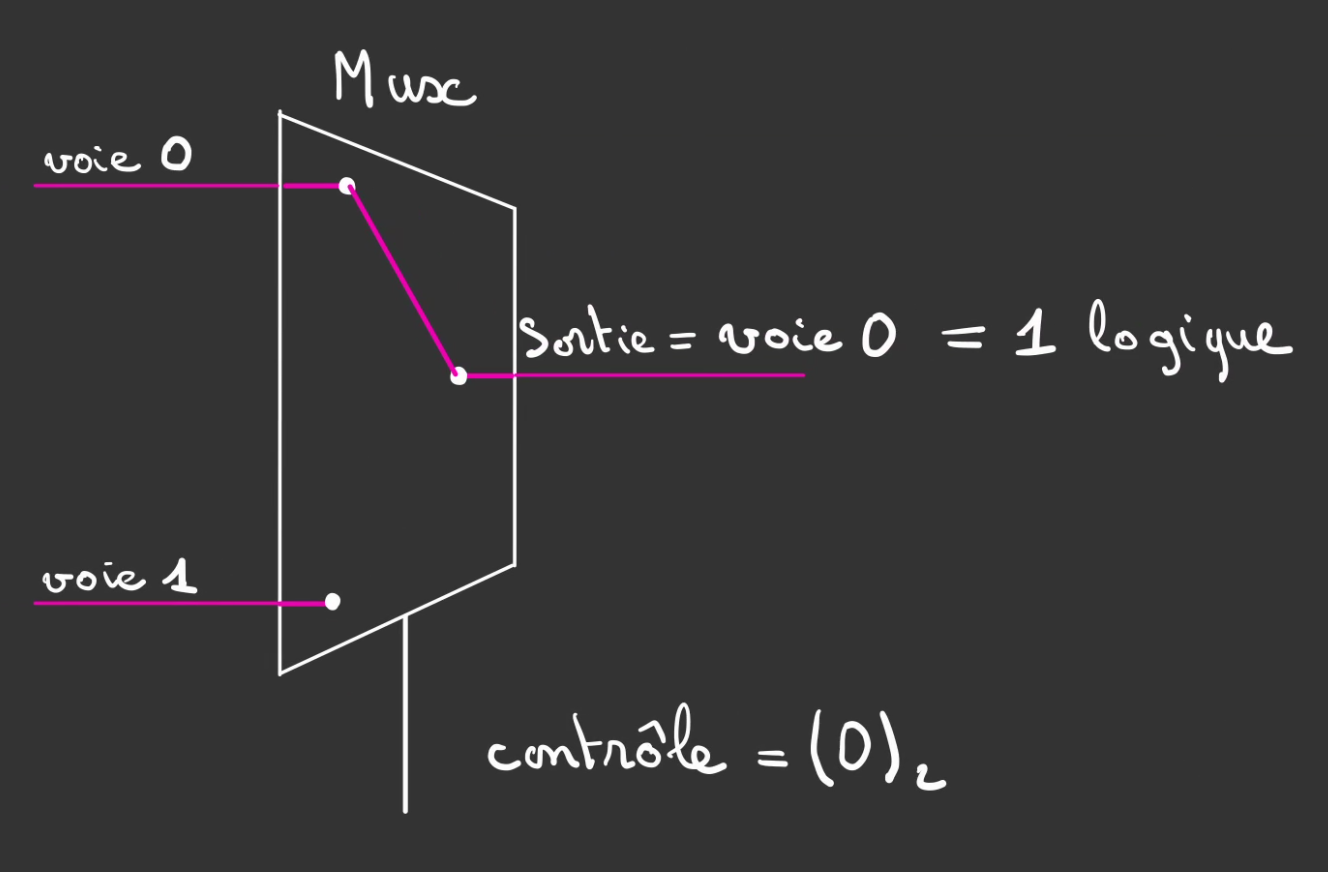

Si la voie 1 possède un signal 1, la Sortie recopie ce comportement.

Si le signal de contrôle bascule à 0, alors c'est la voie 0 qui est connectée à la Sortie.

La voie 1 même à 1 est ignorée.

De la même manière, si la voie 0 passe à 1, la Sortie vaut 1.

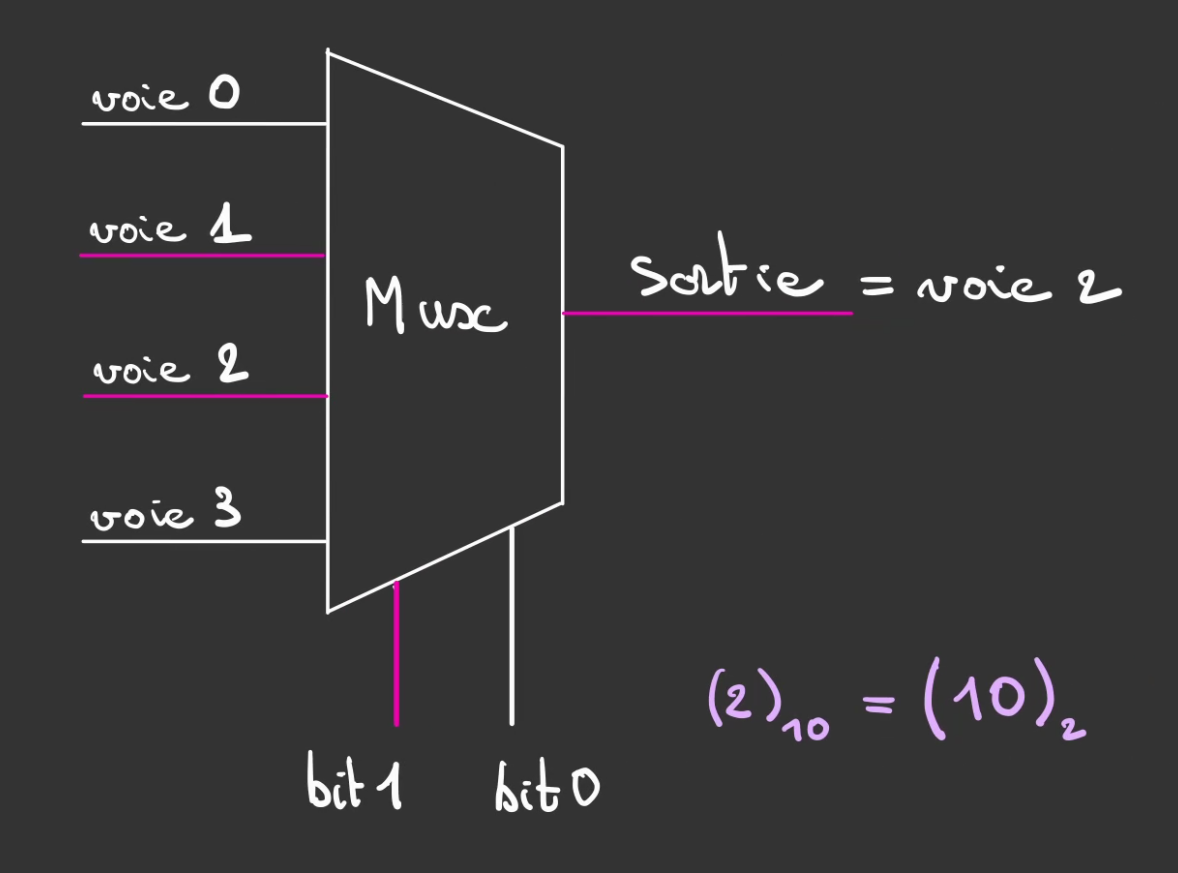

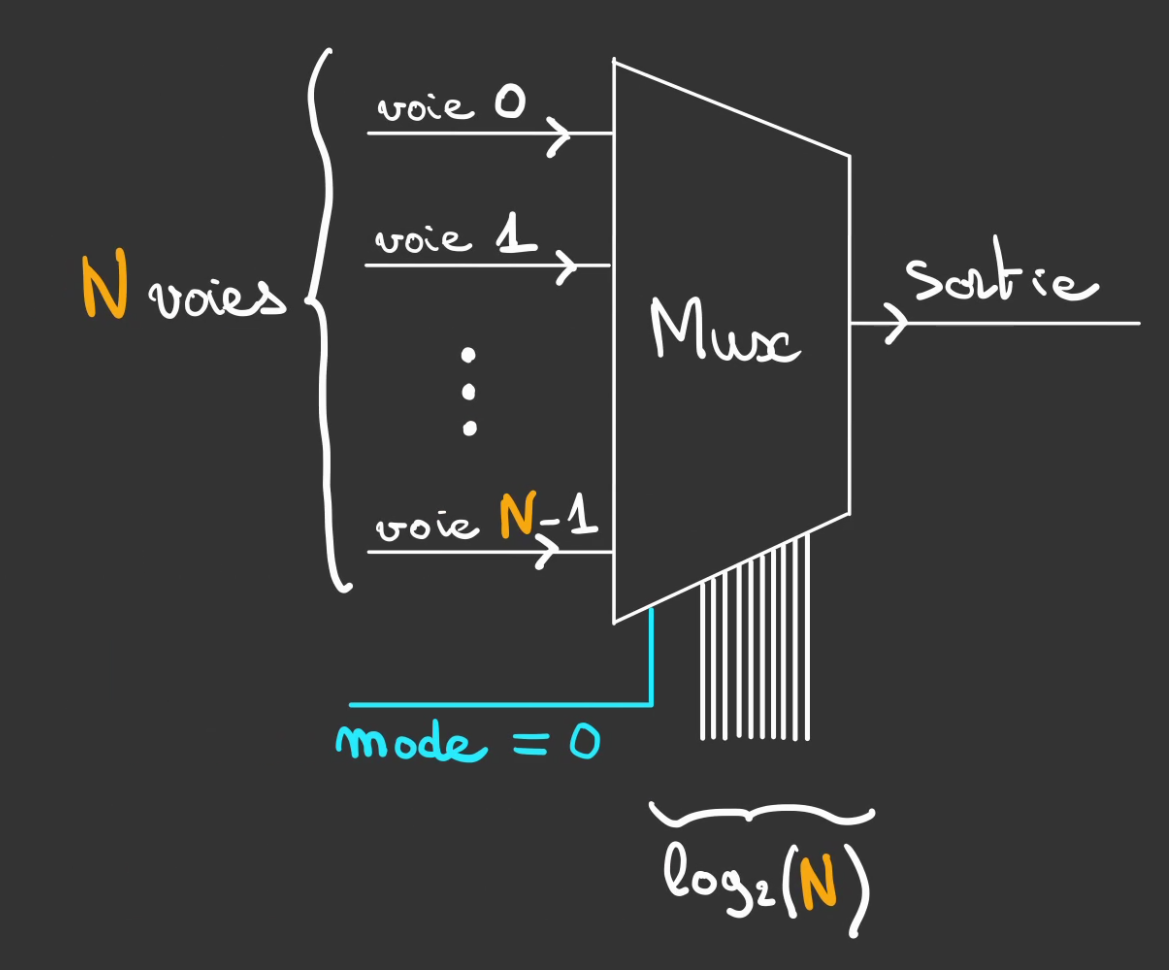

On peut alors utiliser le même système d'adressage que pour le decodeur pour venir connecter plus de 2 voies à une sortie.

On contrôle alors avec autant de bits que nécessaire, ici 2 pour contrôler 4 voies.

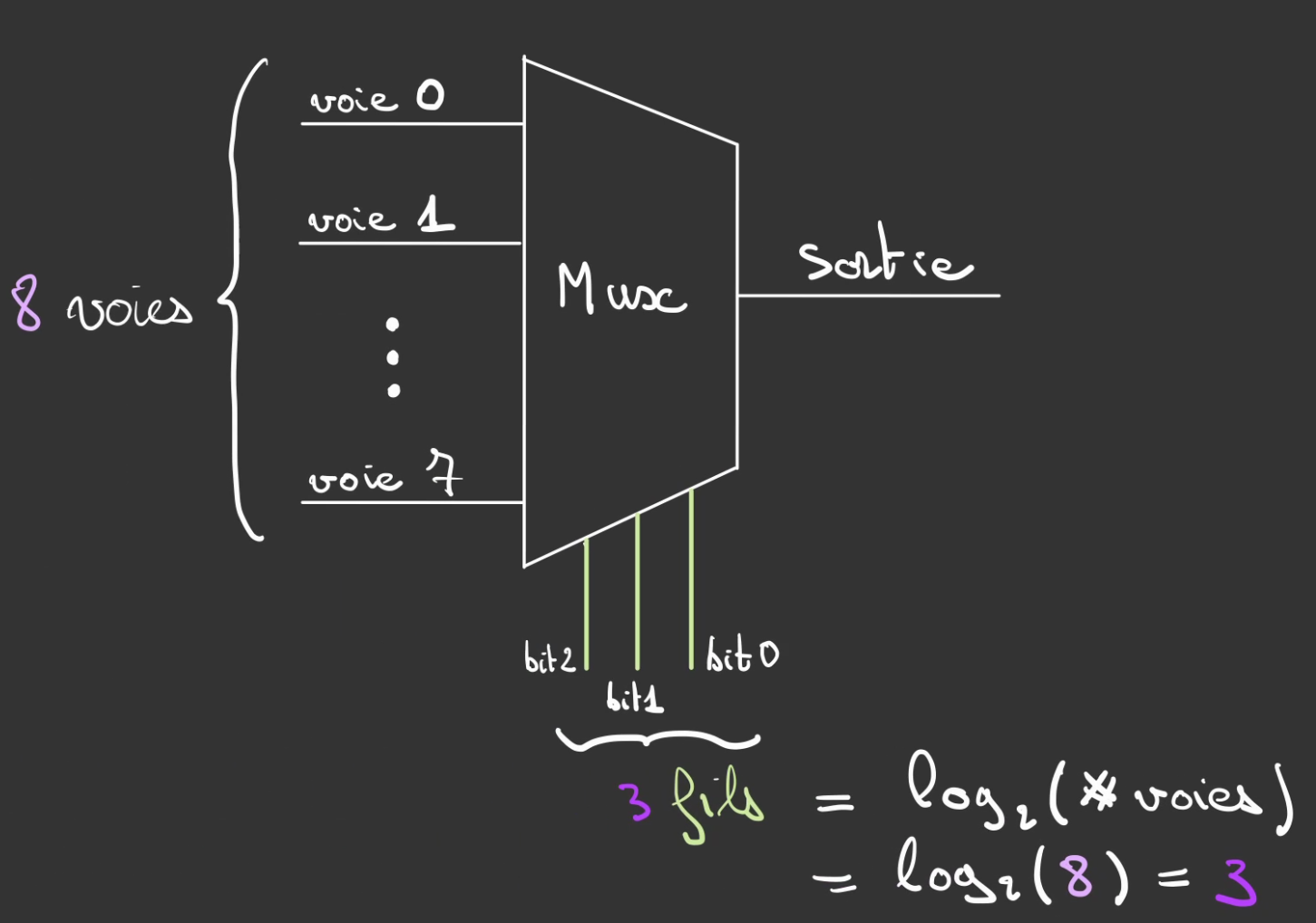

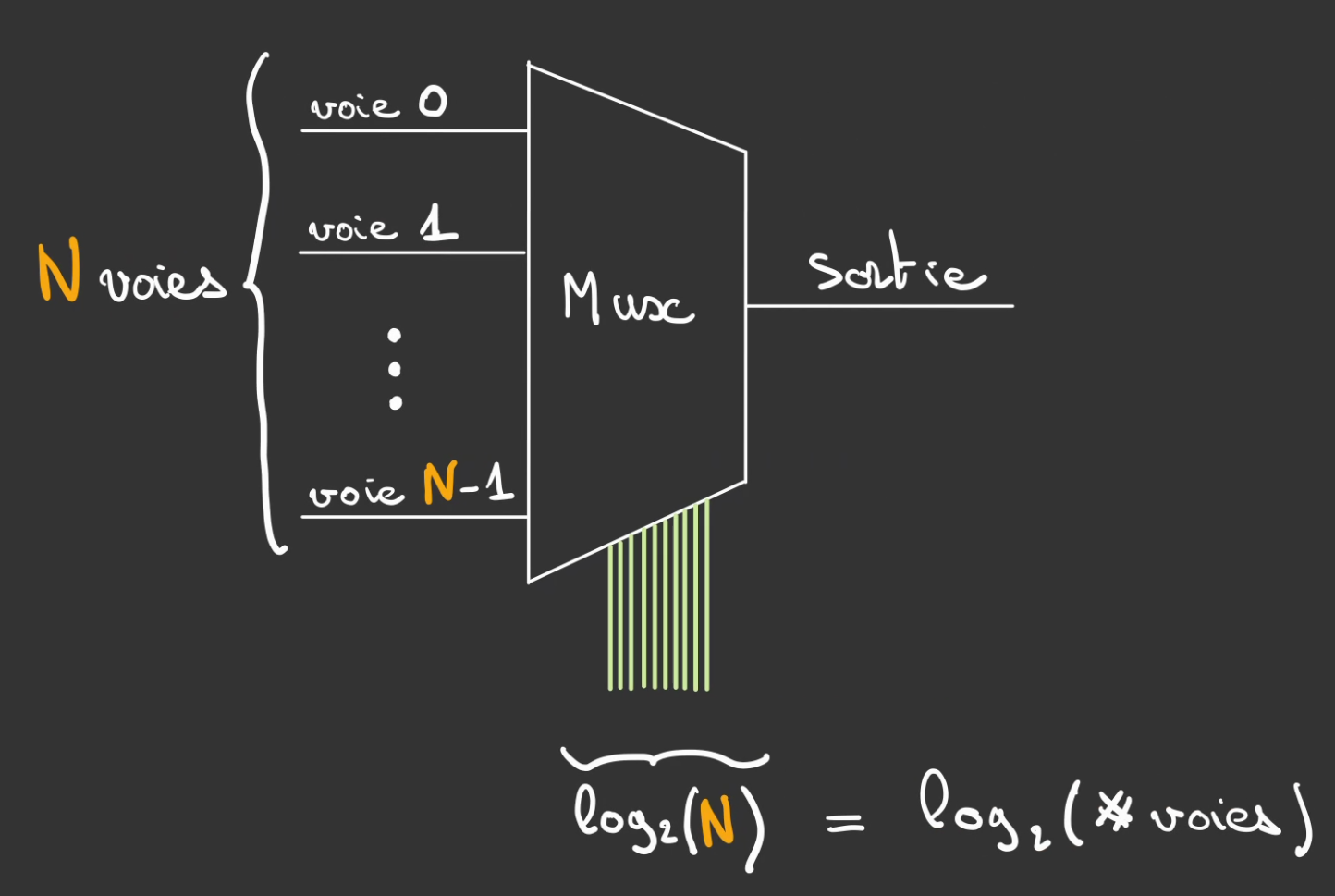

Et on peut venir augmenter le nombre de voies.

Et finalement généraliser à N voies.

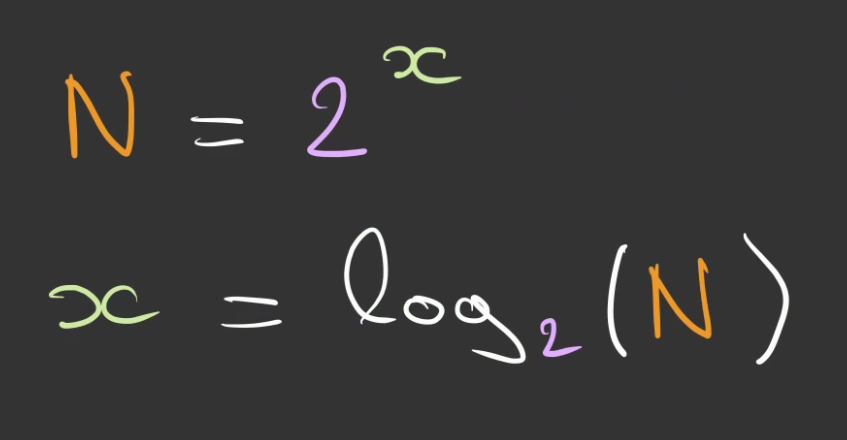

Pour déterminer le nombre de fils de contrôle nécessaires. On va poser deux choses :

- soit x le nombre de fils de contrôle

- soit N le nombre de voies

On voit aussi que le nombre de voies sera toujours une puissance de 2.

Ce système ce nomme un multiplexeur.

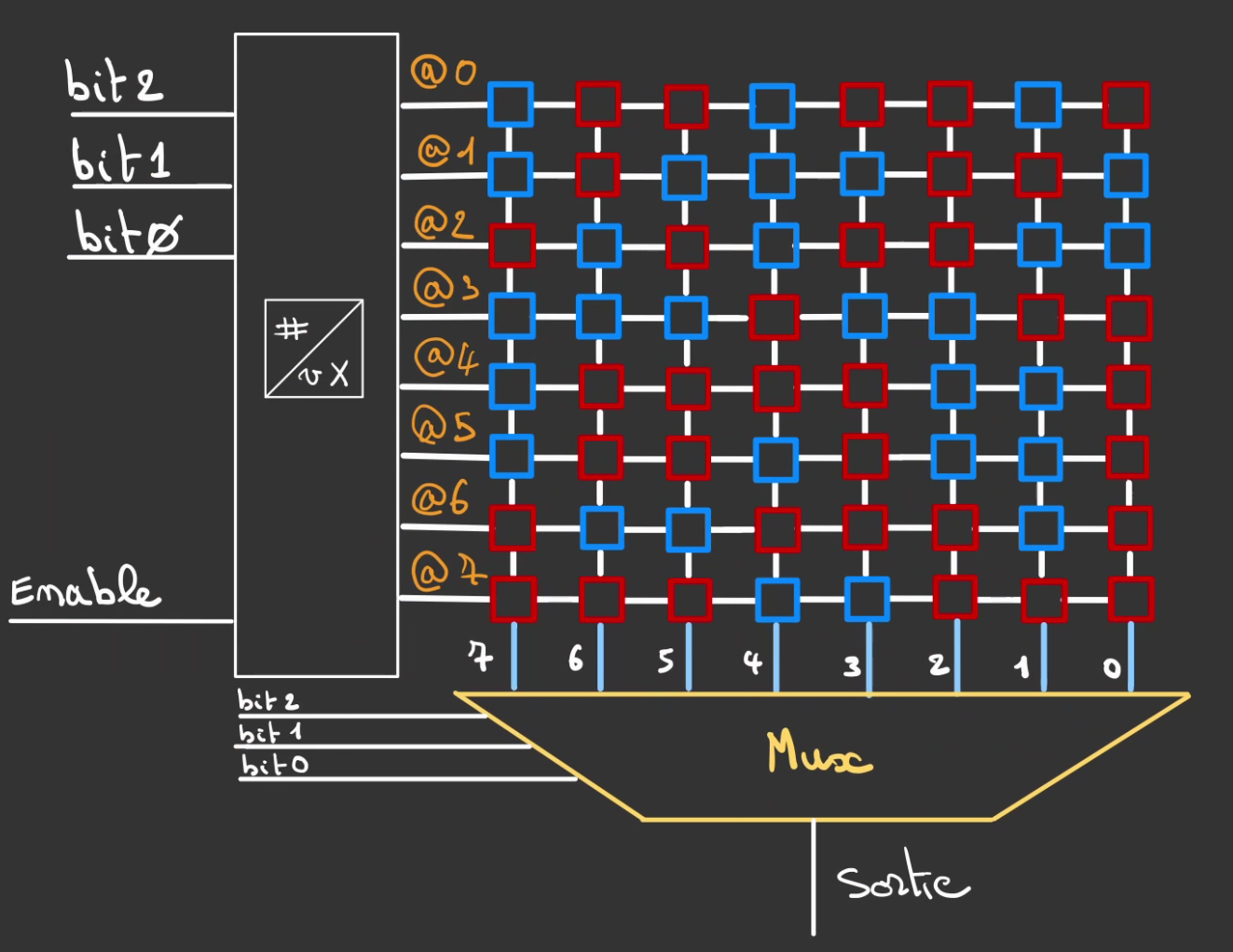

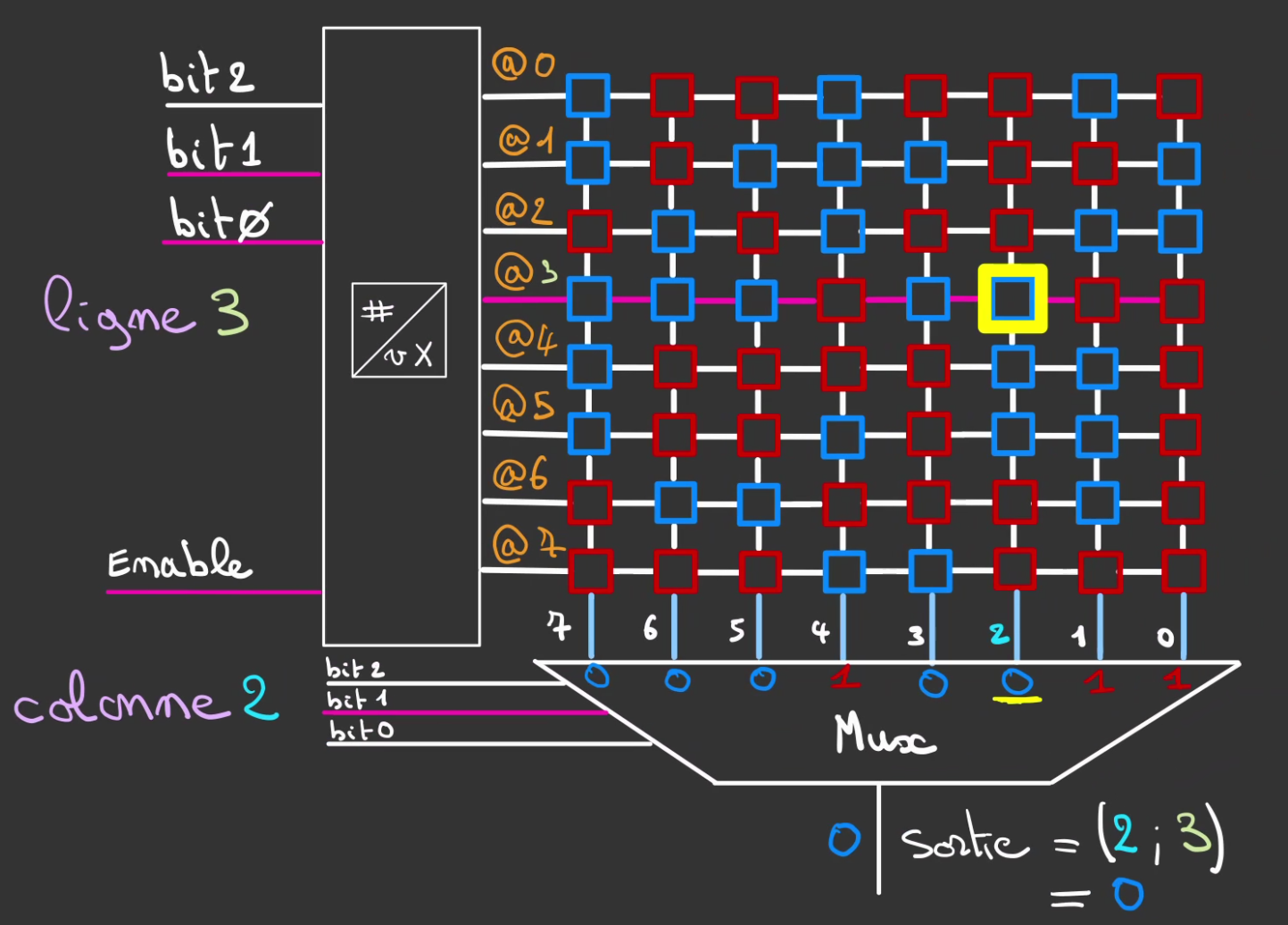

Selection de la colonne

Notre système précédent avait comme problème le faible stockage.

On a aussi vu que l'on ne pouvait pas faire grandir en largeur notre matrice, car la taille du bus de données auquel la matrice est rattachée doit rester raisonnable.

L'idée qui semble moins optimisée va être de selectionner une unique cellule et plus toute la largeur.

Ainsi on peut faire grandir la largeur de la matrice indépendamment de la largeur du bus de données.

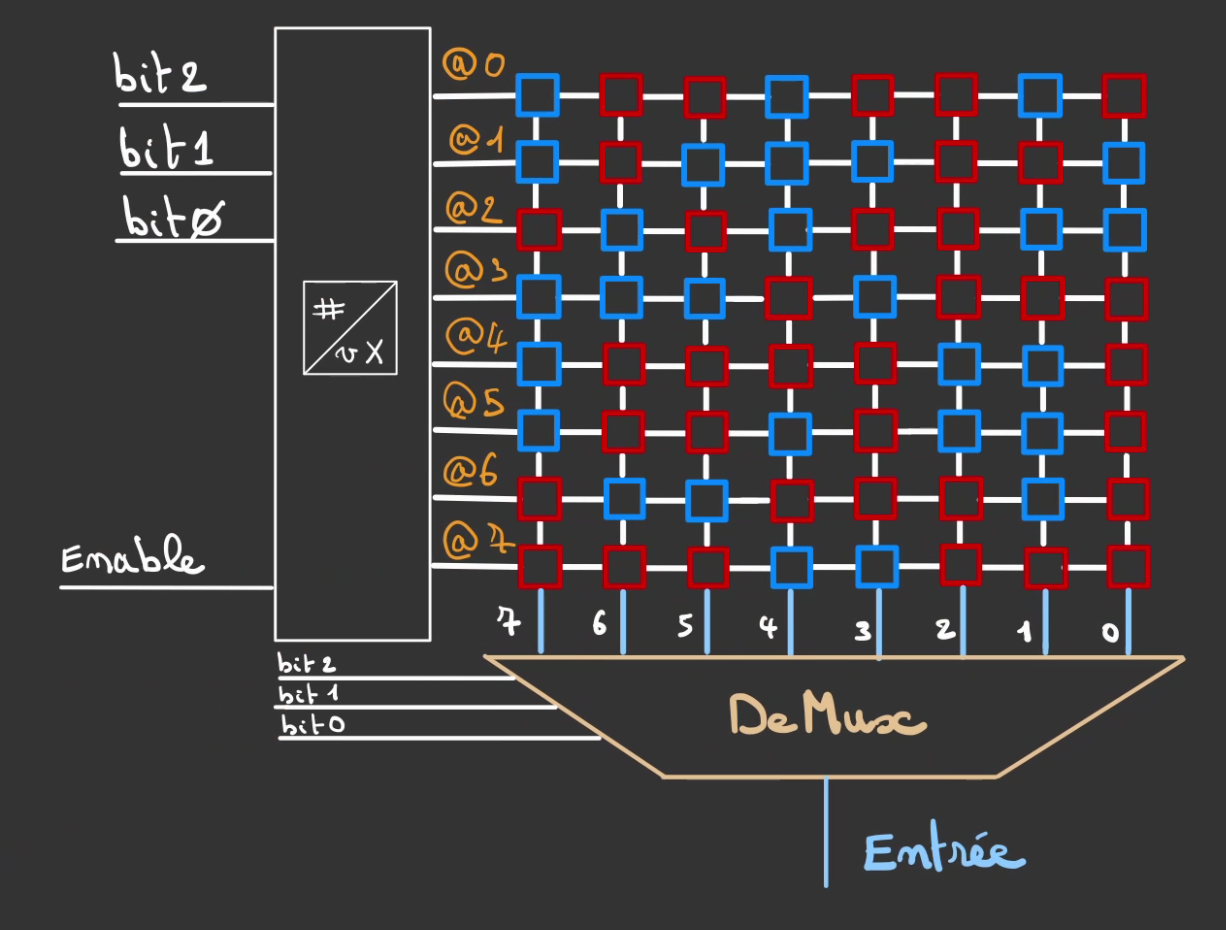

Pour cela on vient brancher un multiplexeur sur la sortie de la matrice.

On branche également des fils de contrôle sur celui-ci.

Ayant 8 bits de données en sortie, nous avons besoin de 3 bits de contrôle.

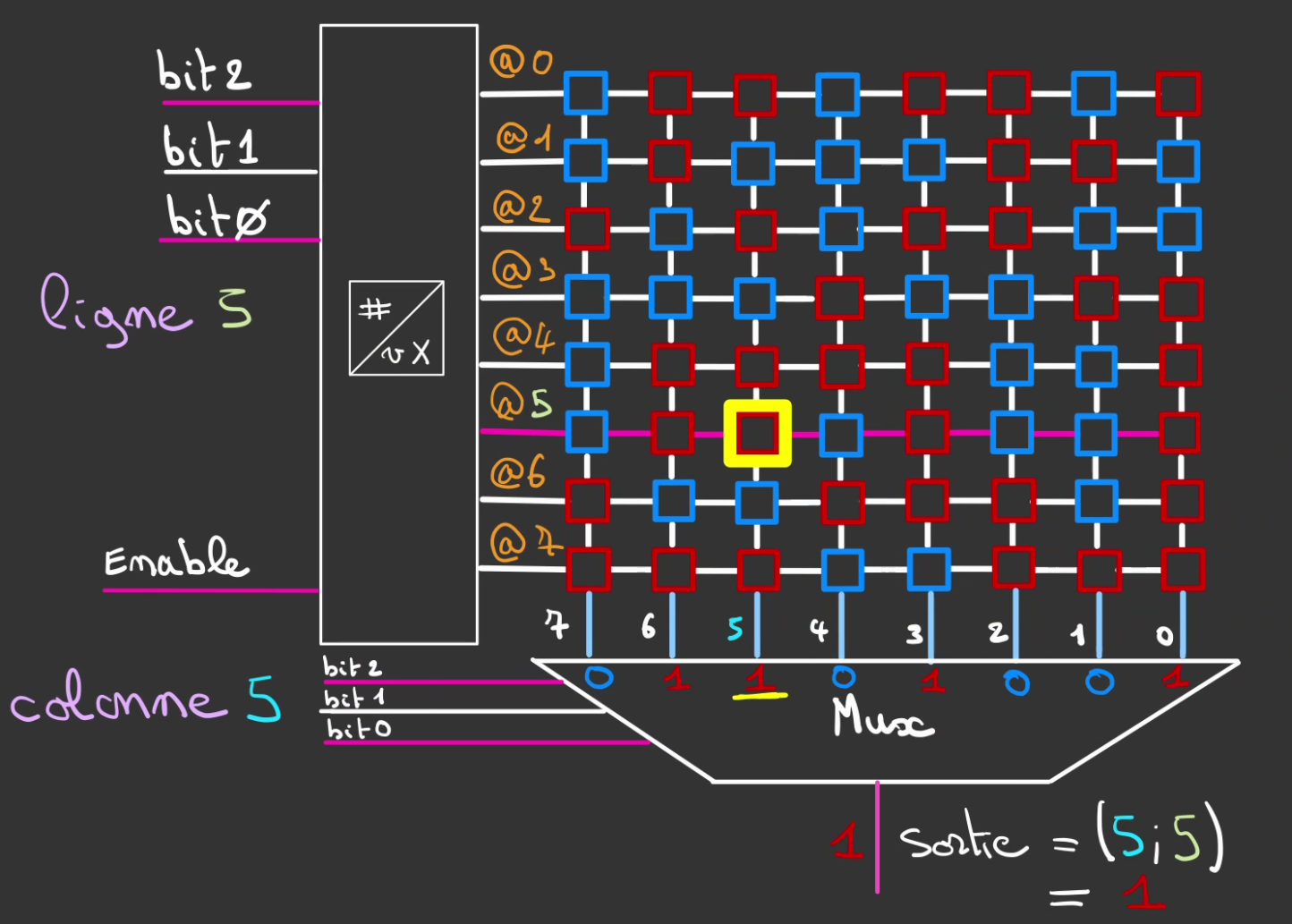

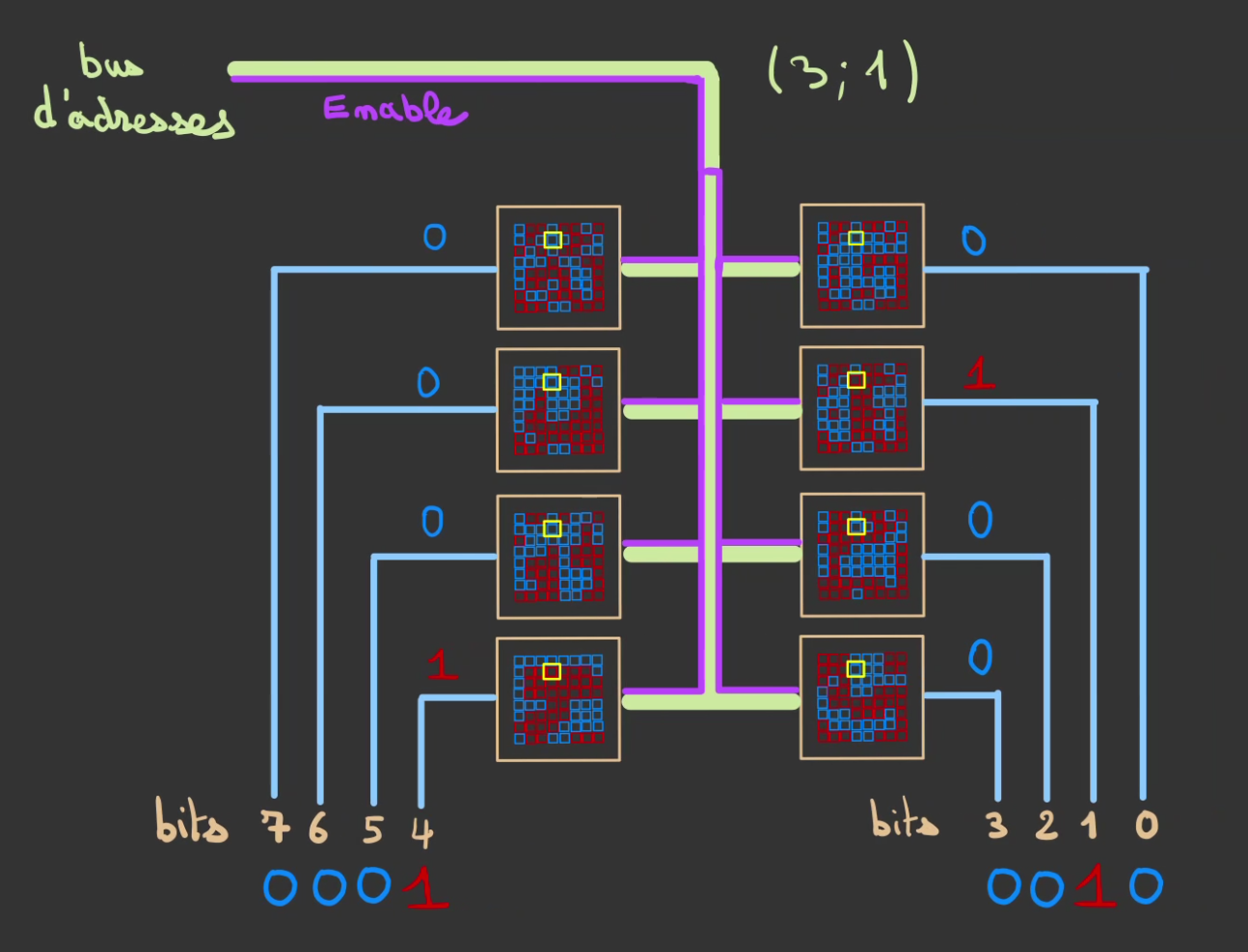

On peut alors sélectionner indépendamment, la ligne et la colonner.

Ici on sélectionne la ligne 5 et la colonne 5.

La case aux coordonnées (5; 5) vaut 1.

Et ainsi la sortie vaut également 1.

On peut alors sélectionner n'importe quelle cellule de la matrice.

Ici les coordonnées (2; 3):

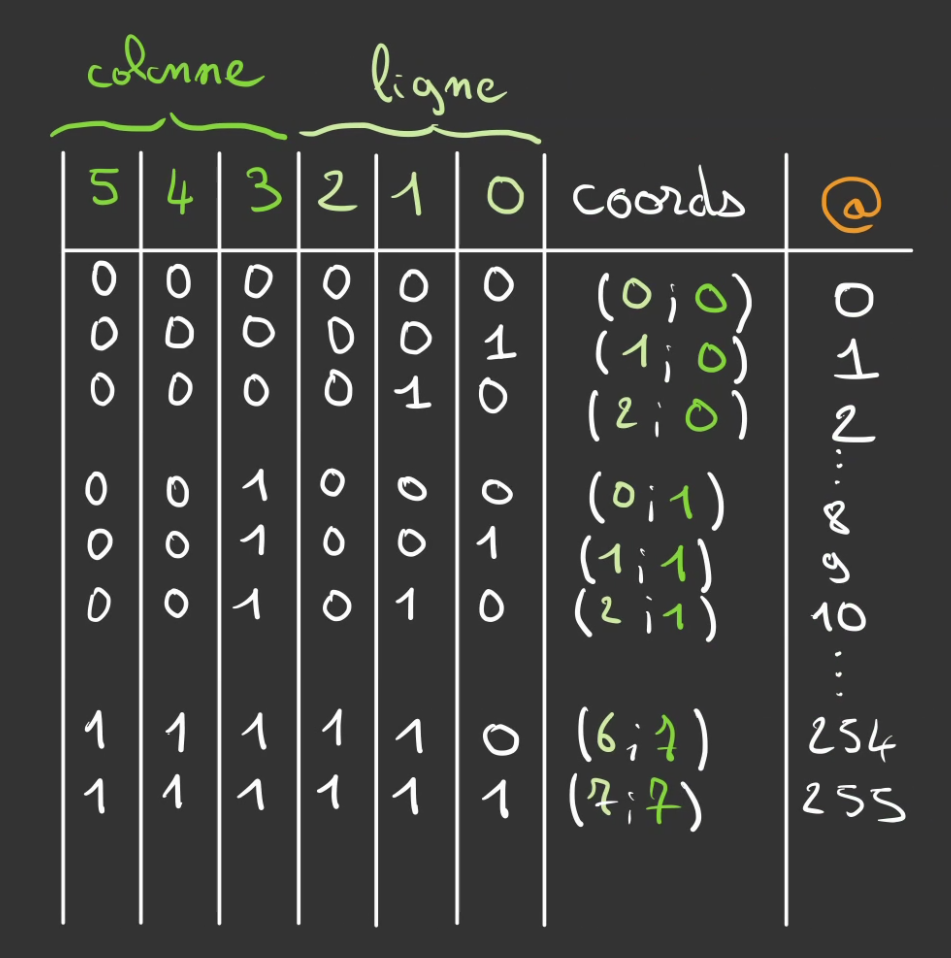

On vient alors diviser notre bus d'adresses entre le décodage de la ligne et la sélection de la colonne.

On peut alors synthétiser en:

On vient d'encapsuler la sélection d'un bit de données.

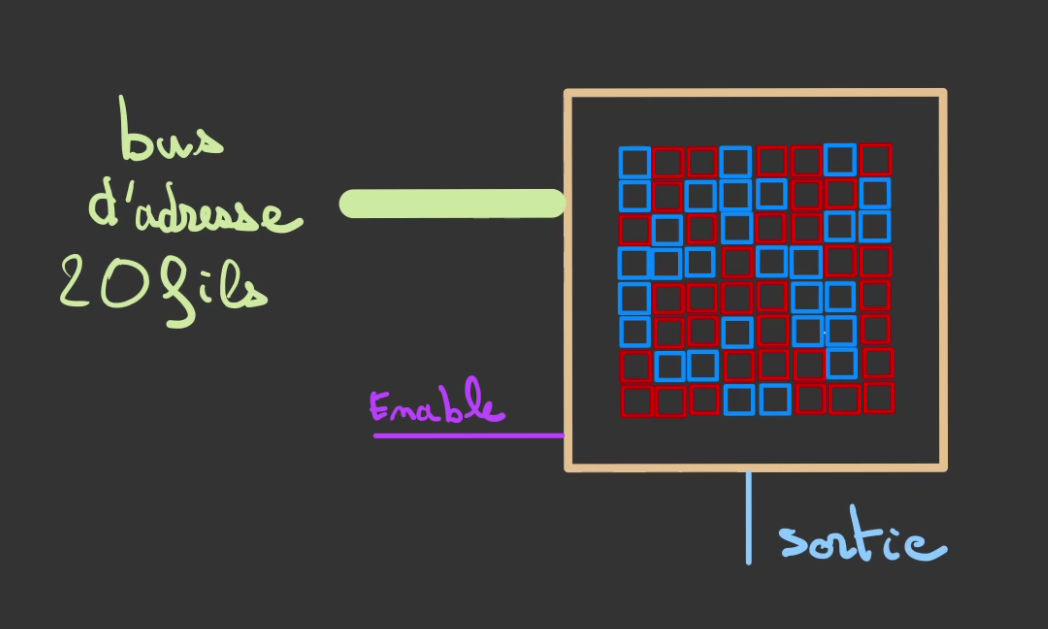

Qui peut se généraliser avec autant de bits du bus d'adresse, ici 20 bits.

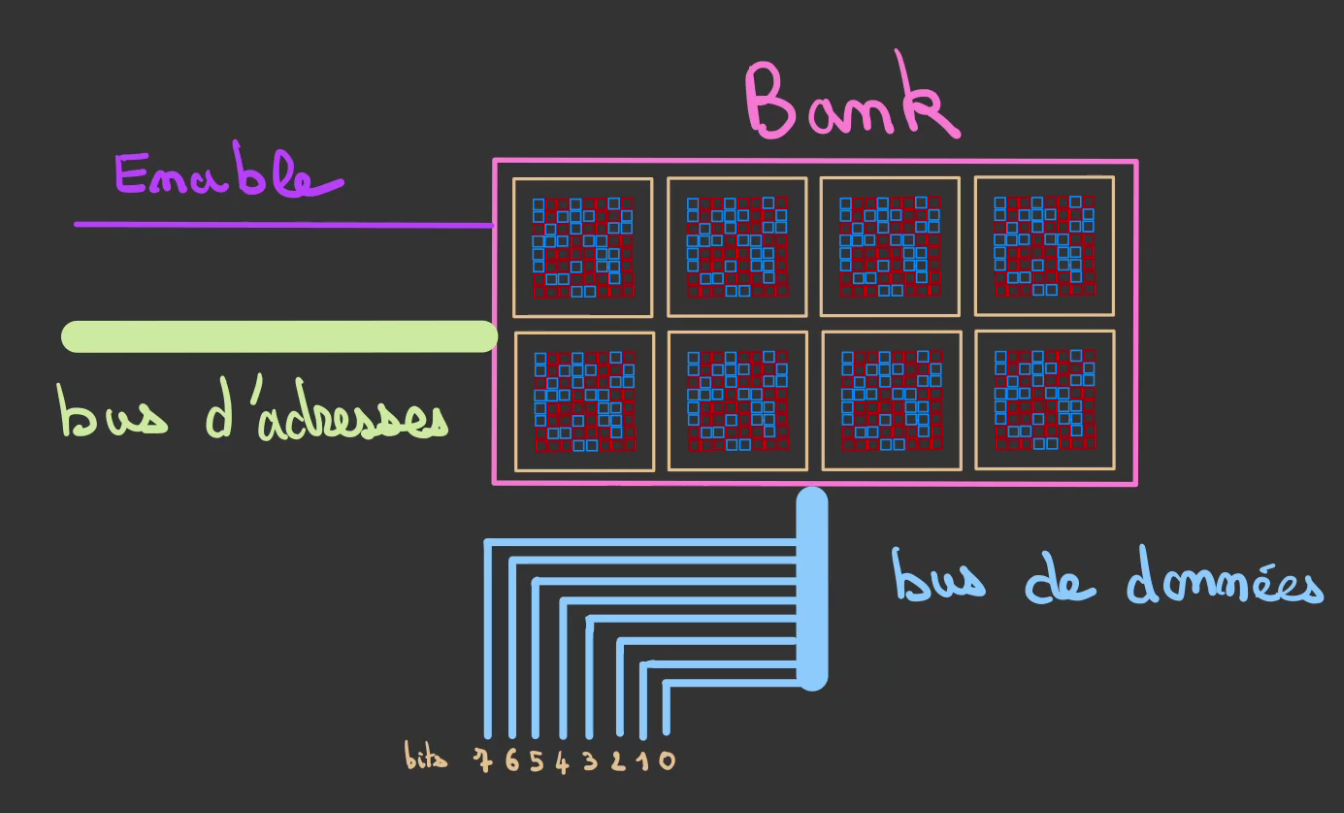

Bank

Pour le moment, nous sommes capable de sélectionner un seul bit.

Or pour créer un octet de donnée. Il nous en faut 8.

L'idée alors est d'utiliser 8 matrices.

Mais de partager le bus d'adresse avec chacune des 8 matrices.

On attribue alors à chaque matrice un bit différent.

Lorsque l'on demande un octet. On vient simultanément sélectionner la même case dans chacune des matrices.

Ainsi l'on récupère notre octet de données.

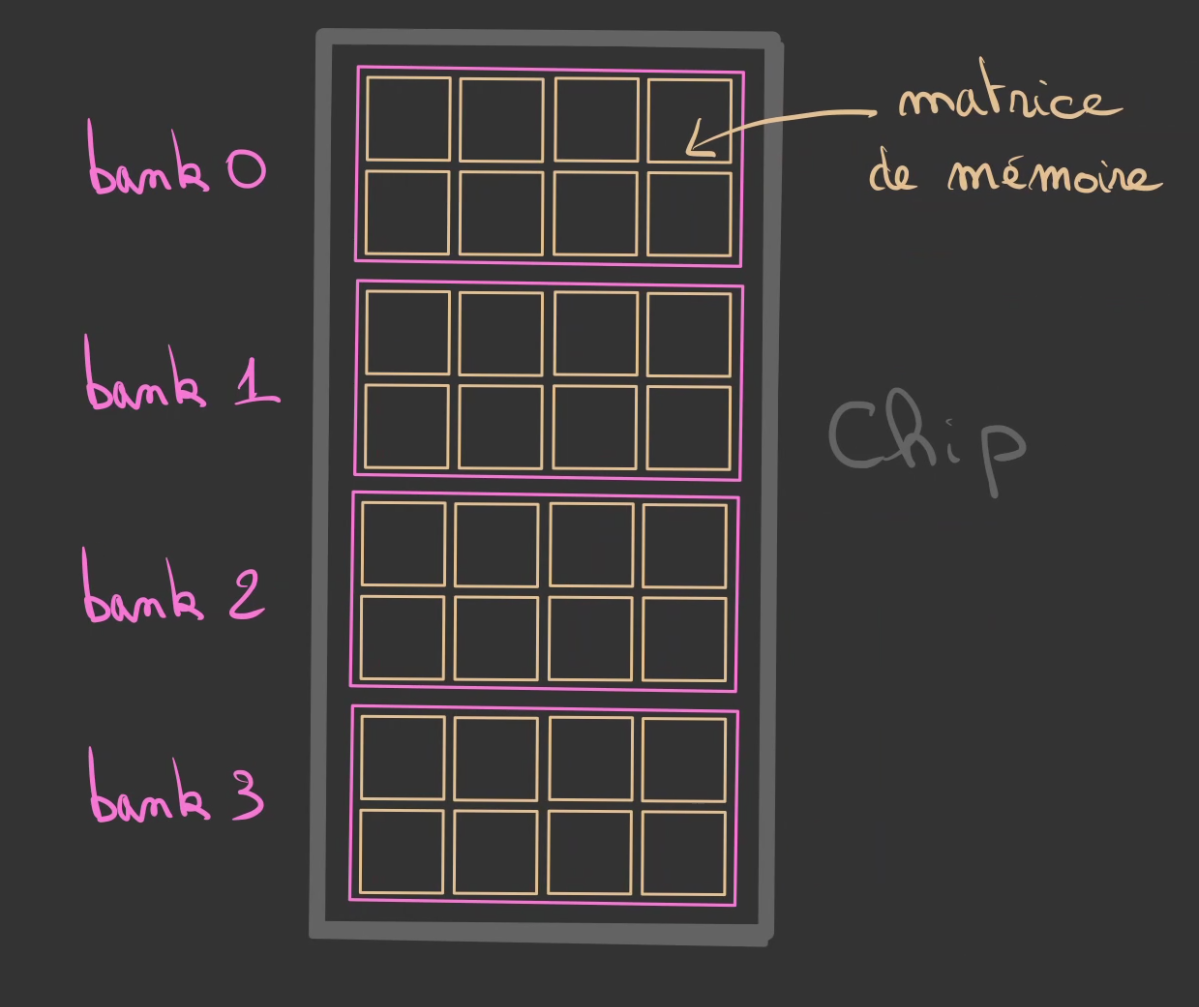

On encapsule alors les 8 matrices dans une bank.

Celle-ci prend en entré le bus d'adresses et en sortie le bus de données.

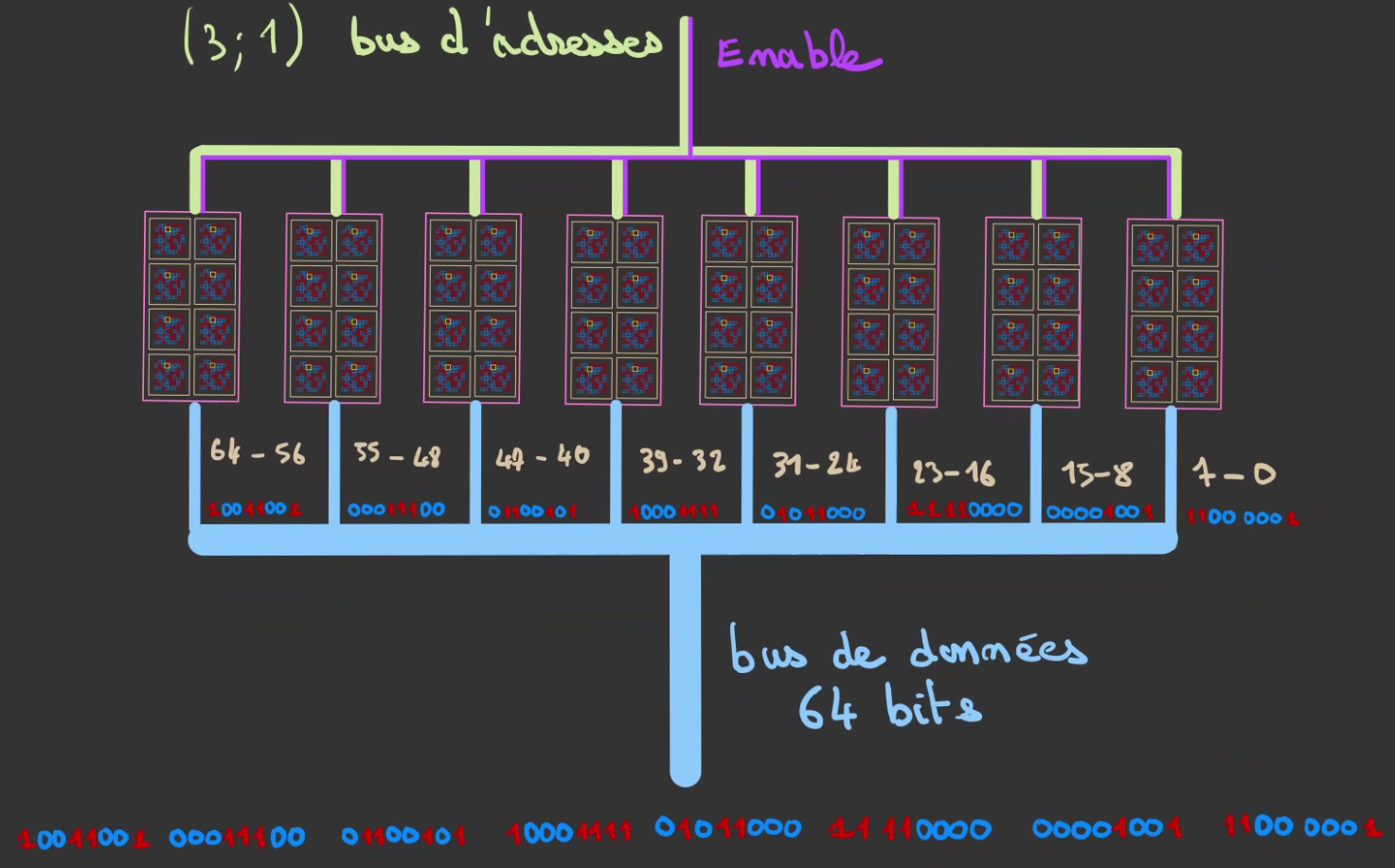

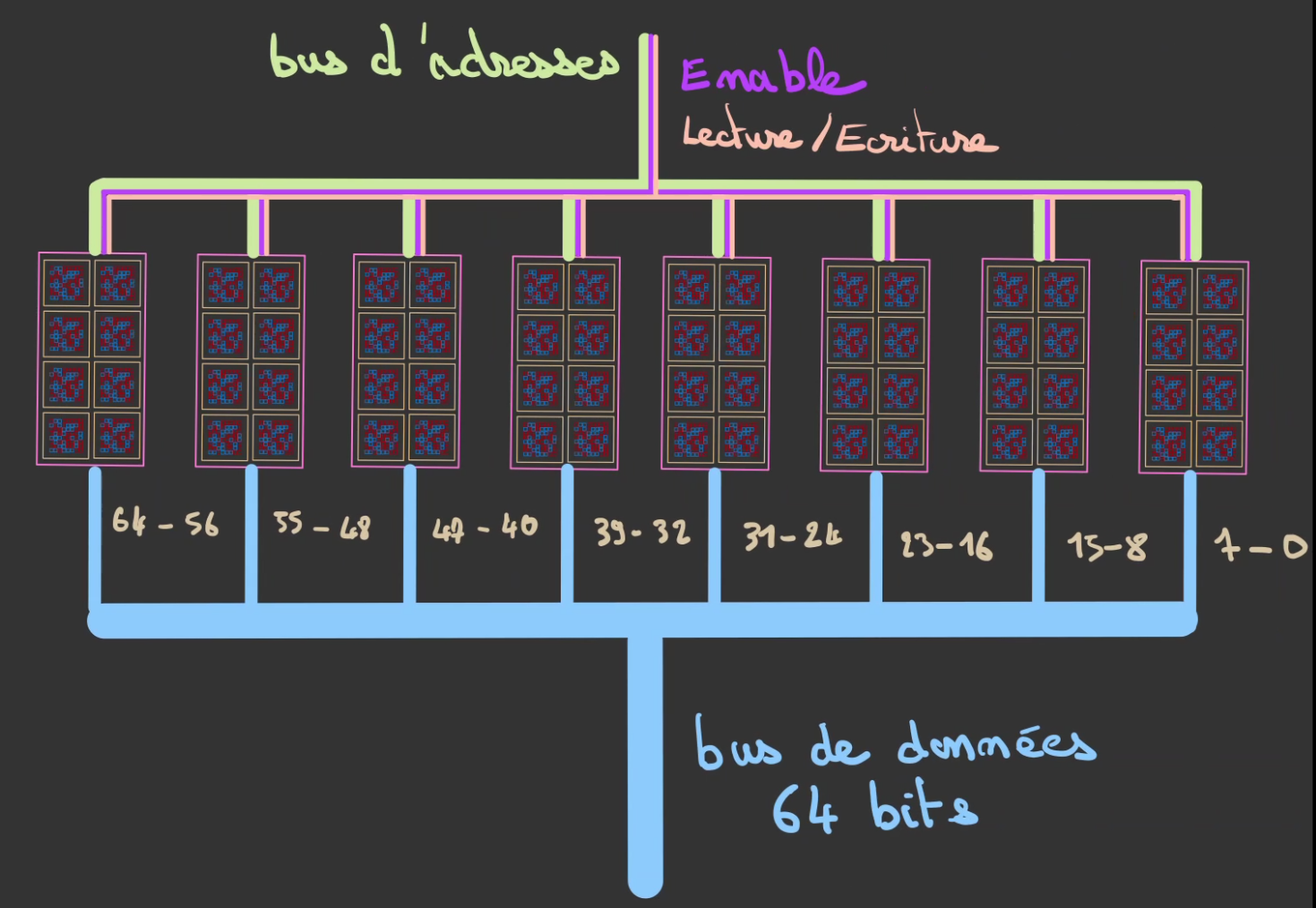

Bus de données complet

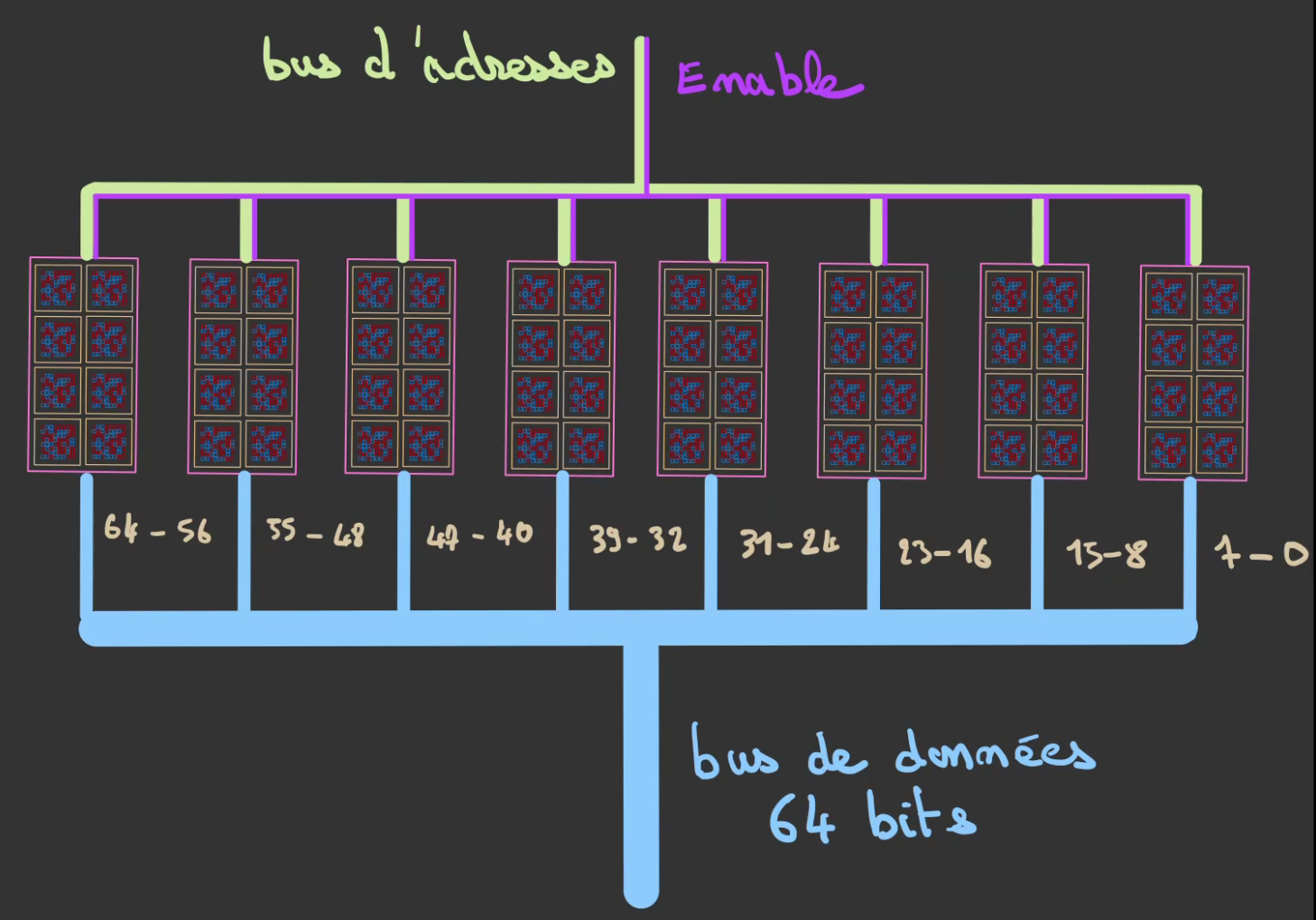

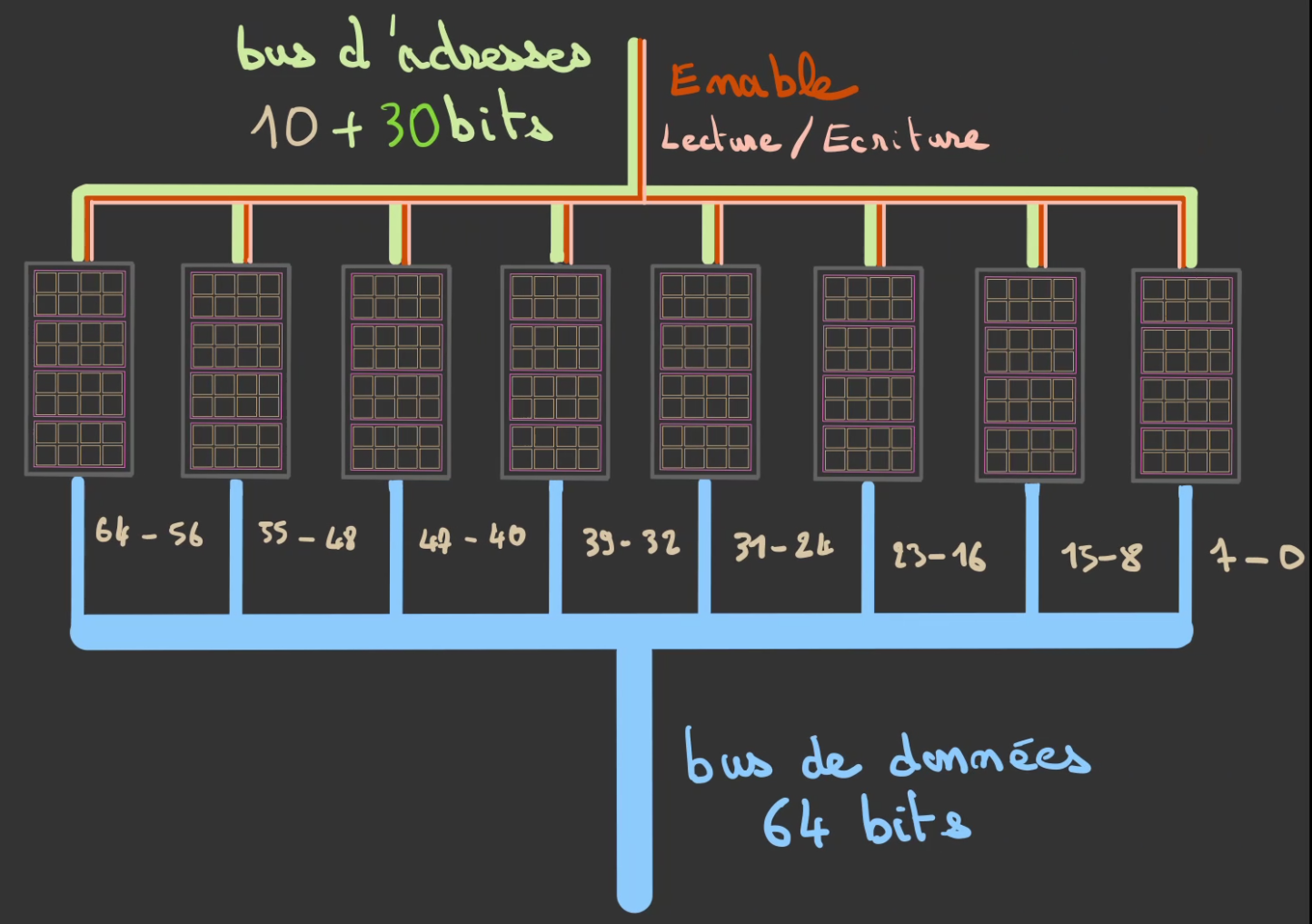

Nous avons récupéré notre octet mais pas les 64 bits que l'on possédait avant.

Nous allons donc continuer à paralléliser les matrices.

Et donc pour se faire, utiliser 8 banks.

On va alors attribuer un octet différent à chaque bank.

On peut alors sélectionner des mots de 64 bits formés par les octets de chaque bank.

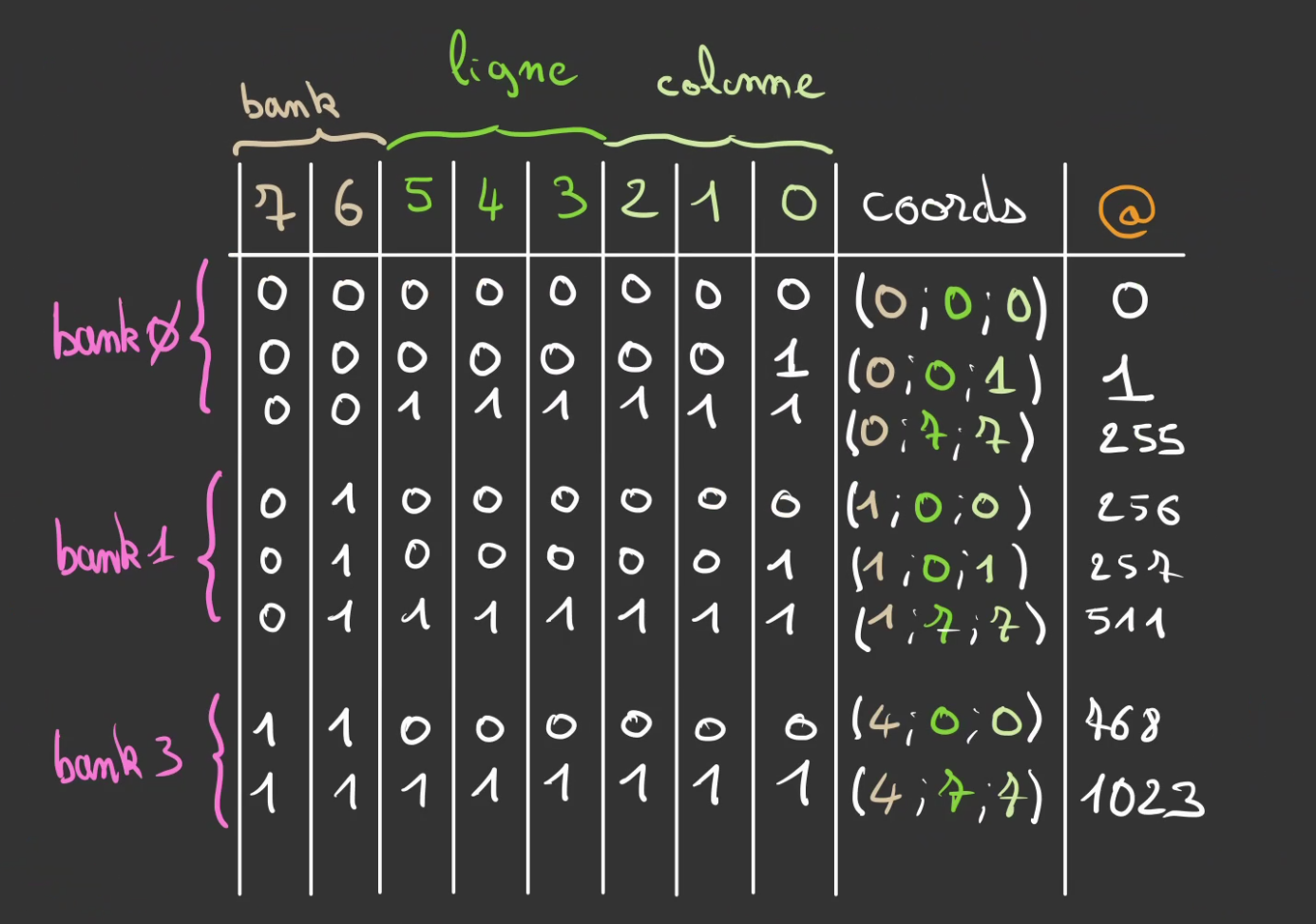

Chaque case des matrices est alors accessible par une adresse unique que l'on peut représenter via ce tableau de correspondance, ici pour un bus d'adresse de 6 bits.

On se retrouve alors virtuellement avec notre système de départ.

Une série de N ligne d'adresses de cases mémoire et aujourd'hui nous savons désormais que chaque case est dans les faits une matrice contenu dans une bank.

La taille de la ligne étant alors la largeur du bus de données. Ici 64 bits. 😀

Stockage

On va voir jusqu'où on peut monter avec notre nouvelle architecture. 😀

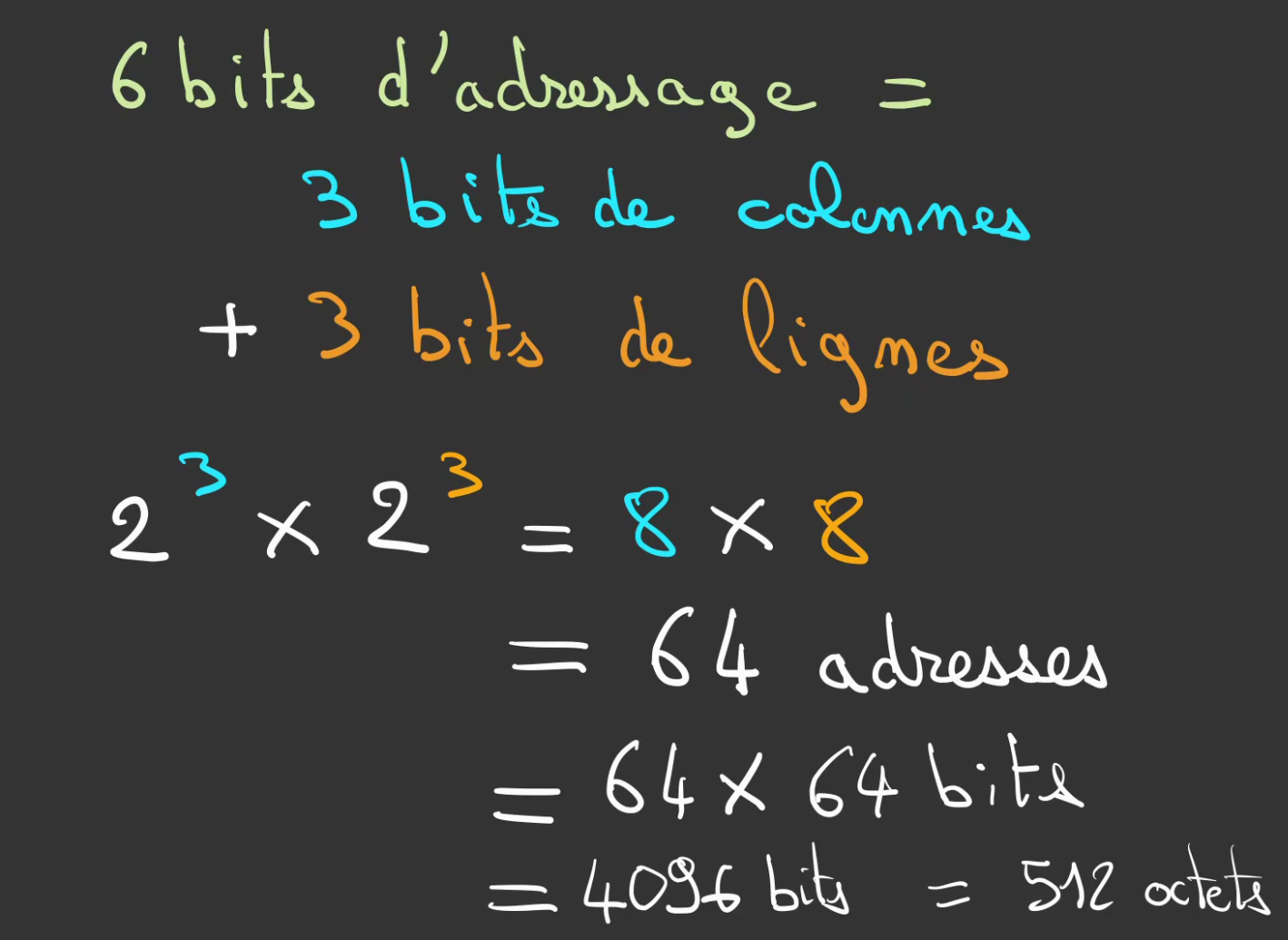

Commençons avec une matrice de 8 par 8.

On obtient un stockage de 512 octets.

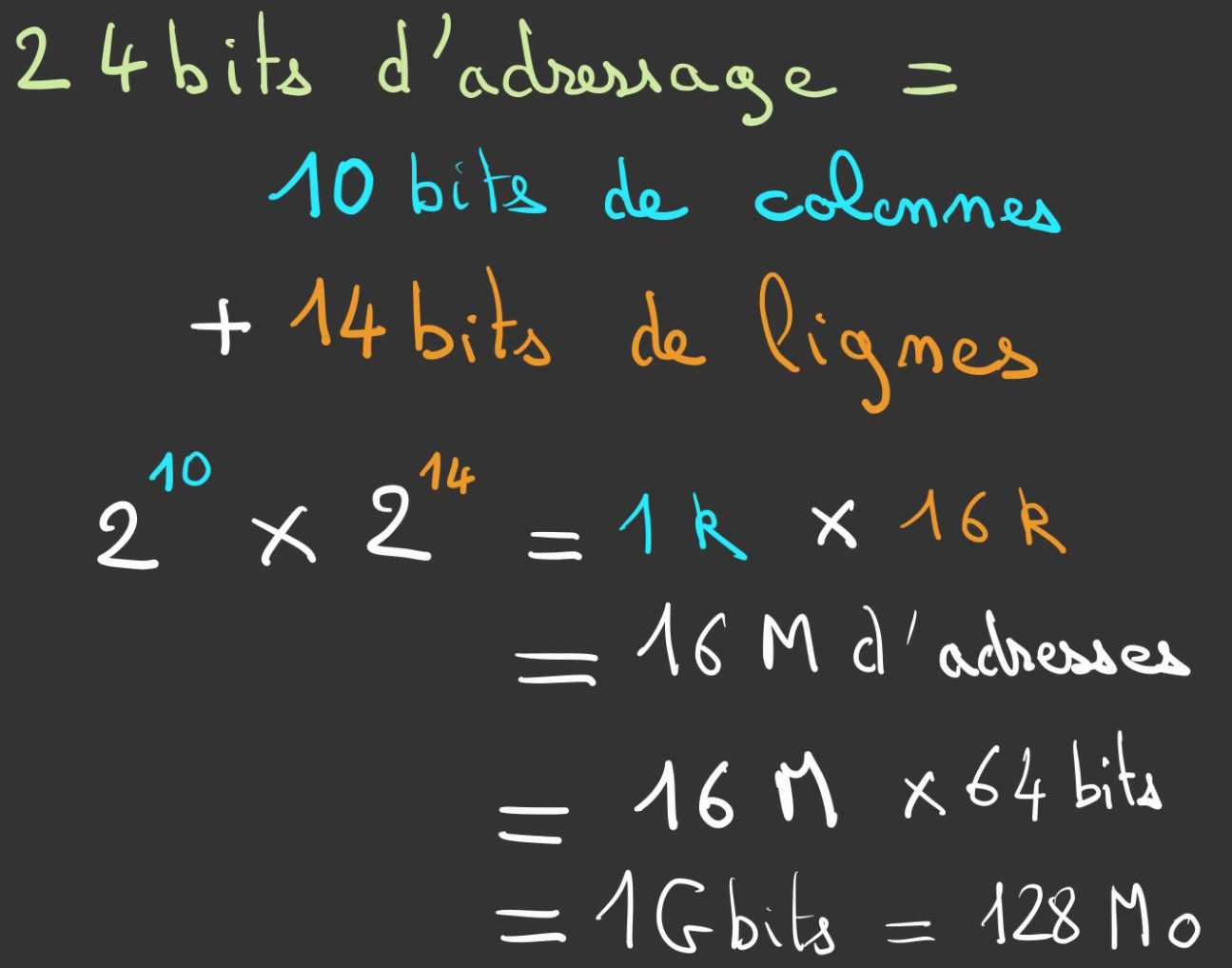

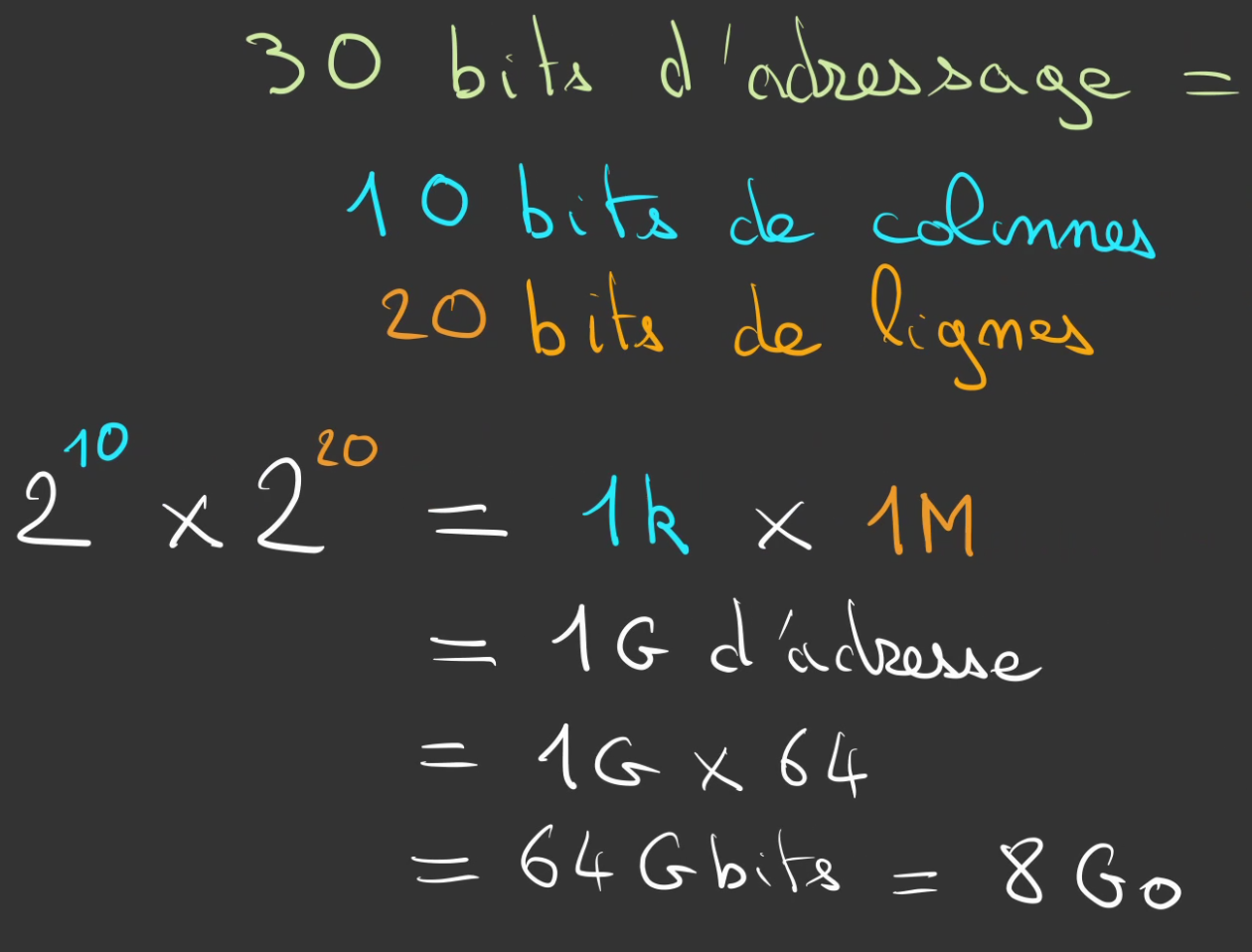

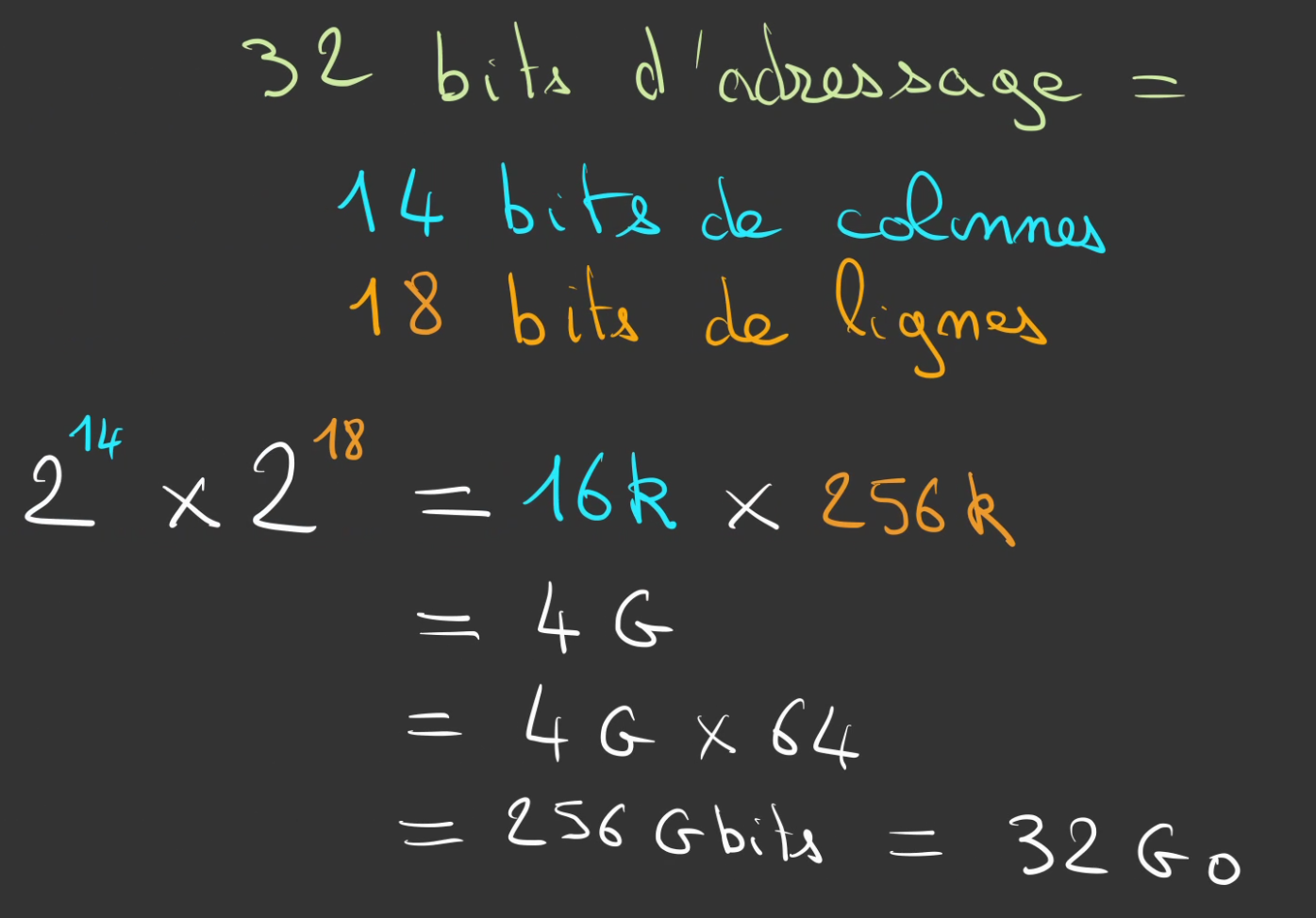

Augmentons la largeur du bus d'adresses à 24 bits.

On utilise alors des matrices rectangulaires de 14 lignes de hauteur et de 10 colonnes de largeur.

On passe alors a 128 Mo de stockage ! 😁

En dissociant la largeur du bus de données de la largeur de la matrice, on a dramatiquement augmenté la densité de stockage.

Vous imaginez si l'on devait gérer 1024 fils !

Et on continue alors à augmenter notre bus de données.

Eh! Mais ça commence à ressembler à ce que l'on connaît. 😉

Maintenant! Le dernier clou dans le cercueil. Rajoutons 2 fils de plus, juste 2...

Faites les calculs pour 40 bits de largeur de bus d'adresse. Vous verrez que vous trouverez quelque chose de massif ! 40 bits d'adressage => 4 To de stockageréponse

Bien sûr l'adressage ne suffit, il faut aussi les cellules mémoire correspondantes et donc les 32 Téra de cellules.

Ceci étant conditionné à la fois par la surface de la mémoire et de la taille de chaque cellules.

Ce qui explique la Loi de Moore appliqué au stockage, plus les cellules seront petites, plus on pourra en caser beaucoup sur une surface réduite!

Ecriture

C'est fantistique on est capable stocker en théorie ce que l'on veut!

En théorie seulement...

Pour le moment, il est impossible d'écrire quoique ce soit en mémoire.

Architecture Von Neumann partie 2

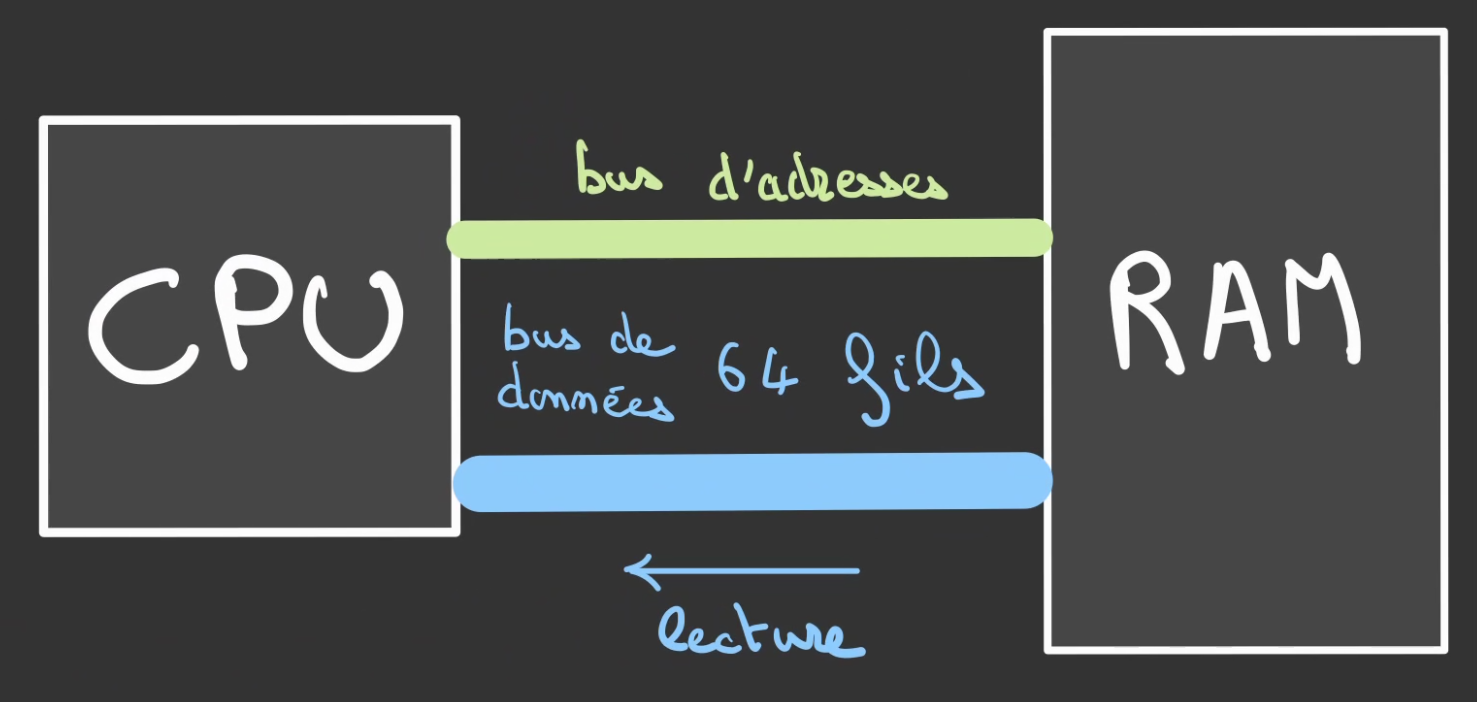

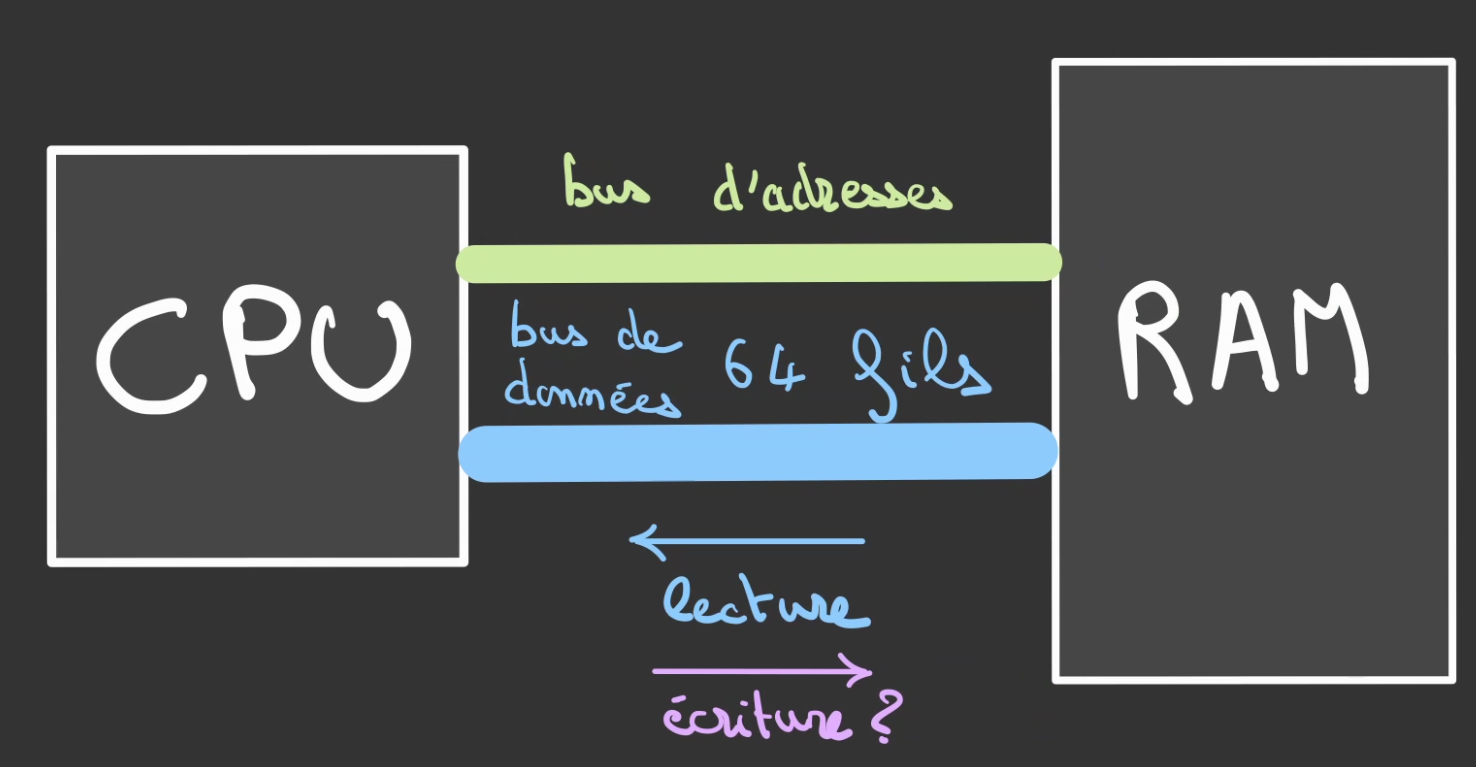

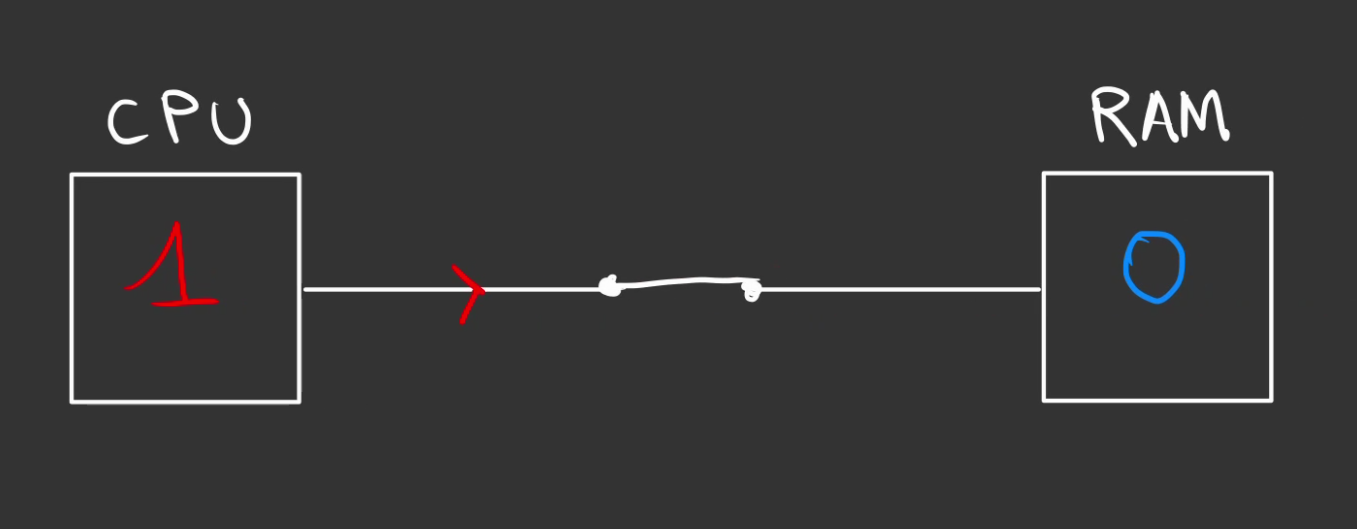

Reprenons le schéma du début.

On a un bus d'adresse de largeur variable et un bus de données de 64 bits.

On peut interroger la mémoire grâce au bus d'adresse et lire la réponse grâce au bus de données.

Par contre, comment peut-on écrire dans cette mémoire ?

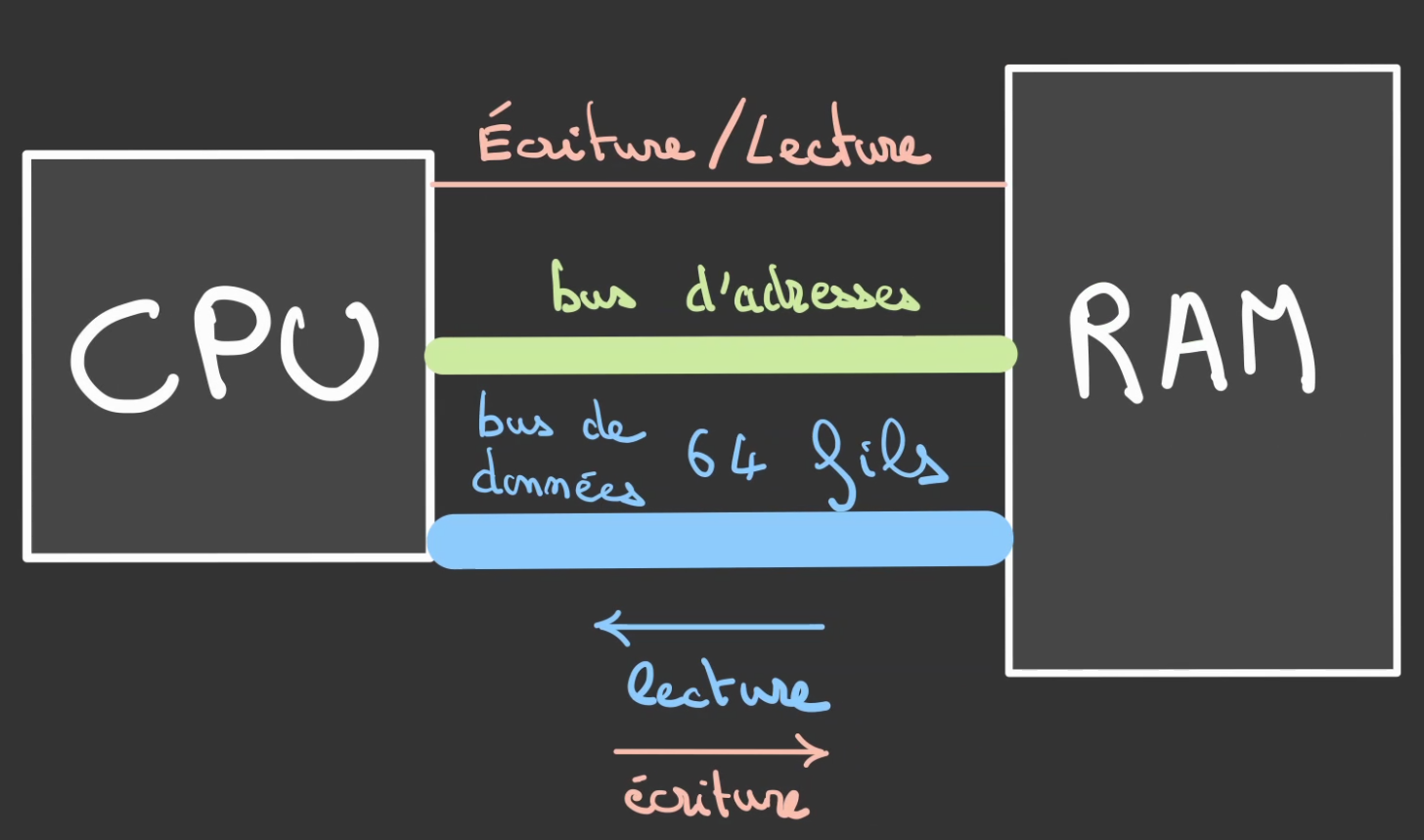

Et bien, nous allons rajouter un nouveau fil !

Celui-ci sera responsable de définir si l'on désire lire depuis une adresse ou y écrire.

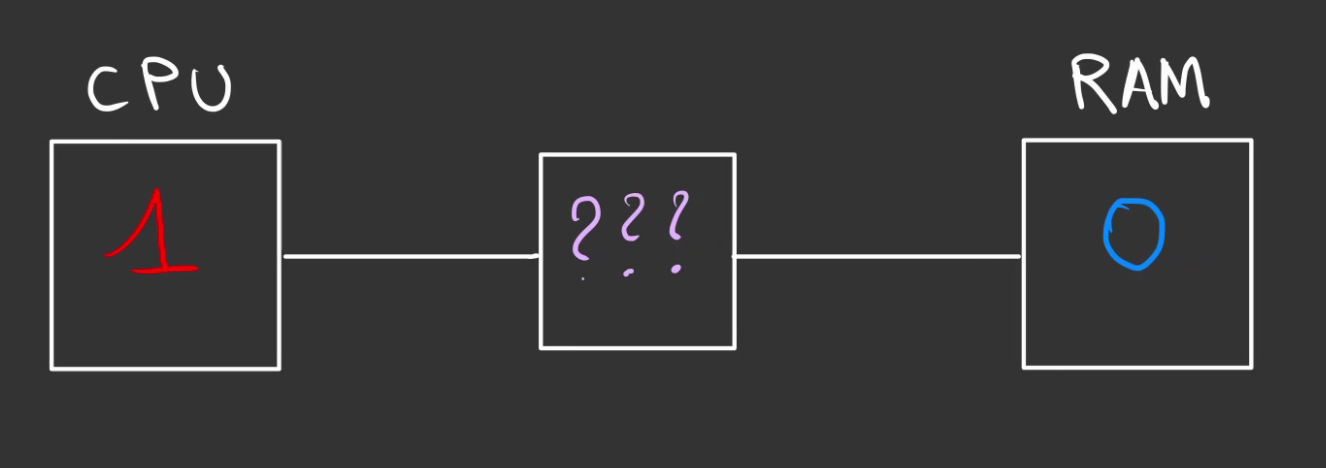

Avant de pouvoir nous attaquer à l'écriture, nous avons besoin de plusieurs outils.

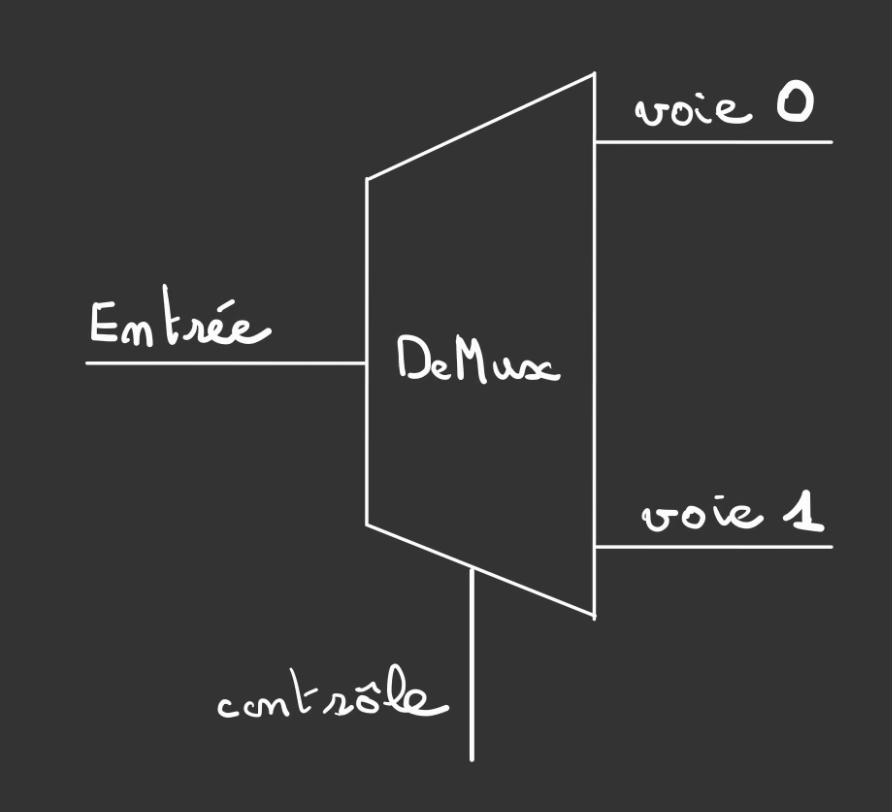

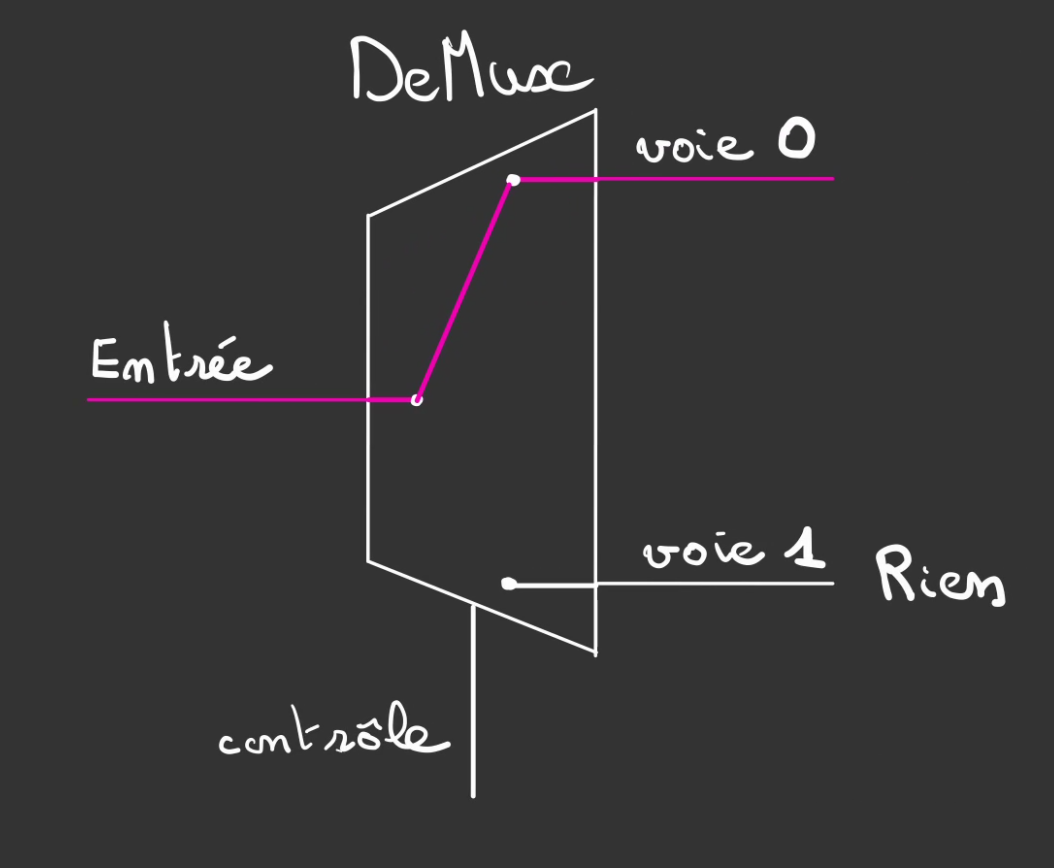

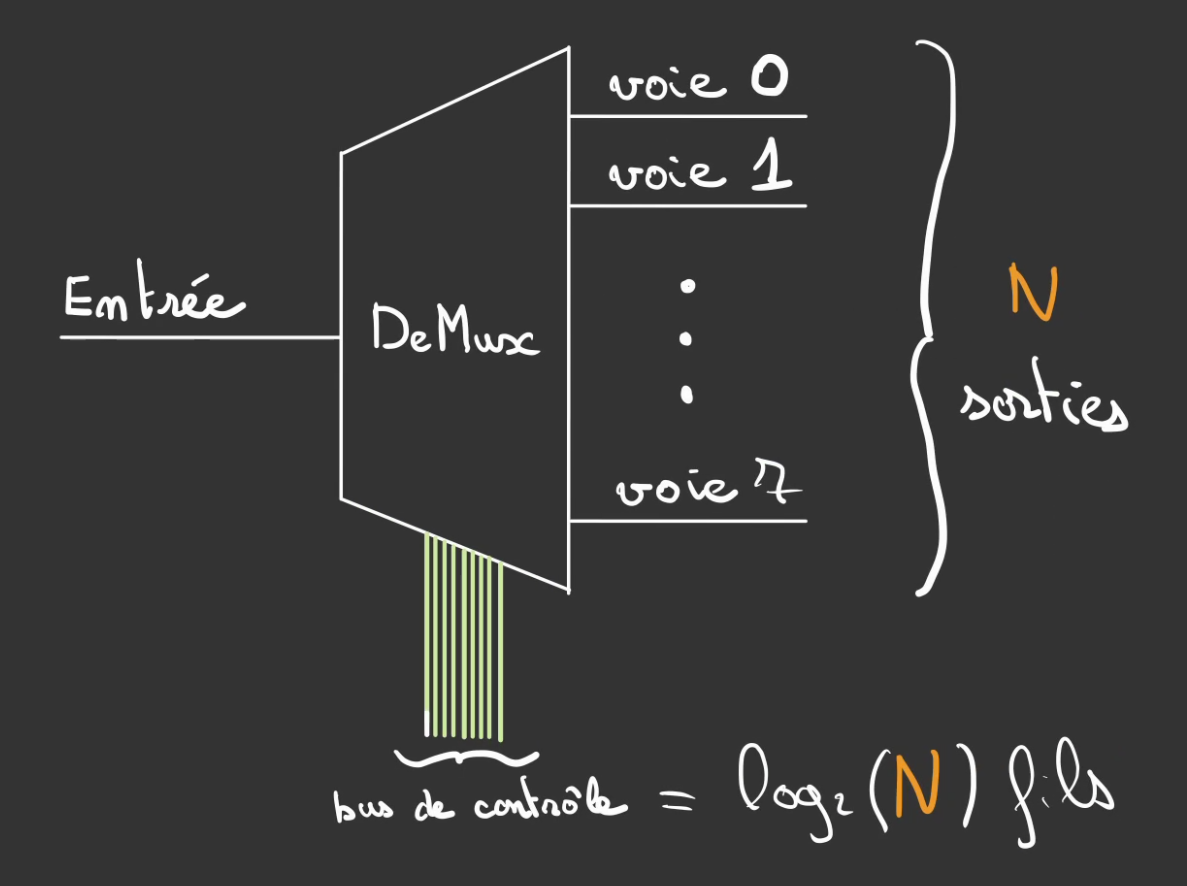

Demultiplexeur

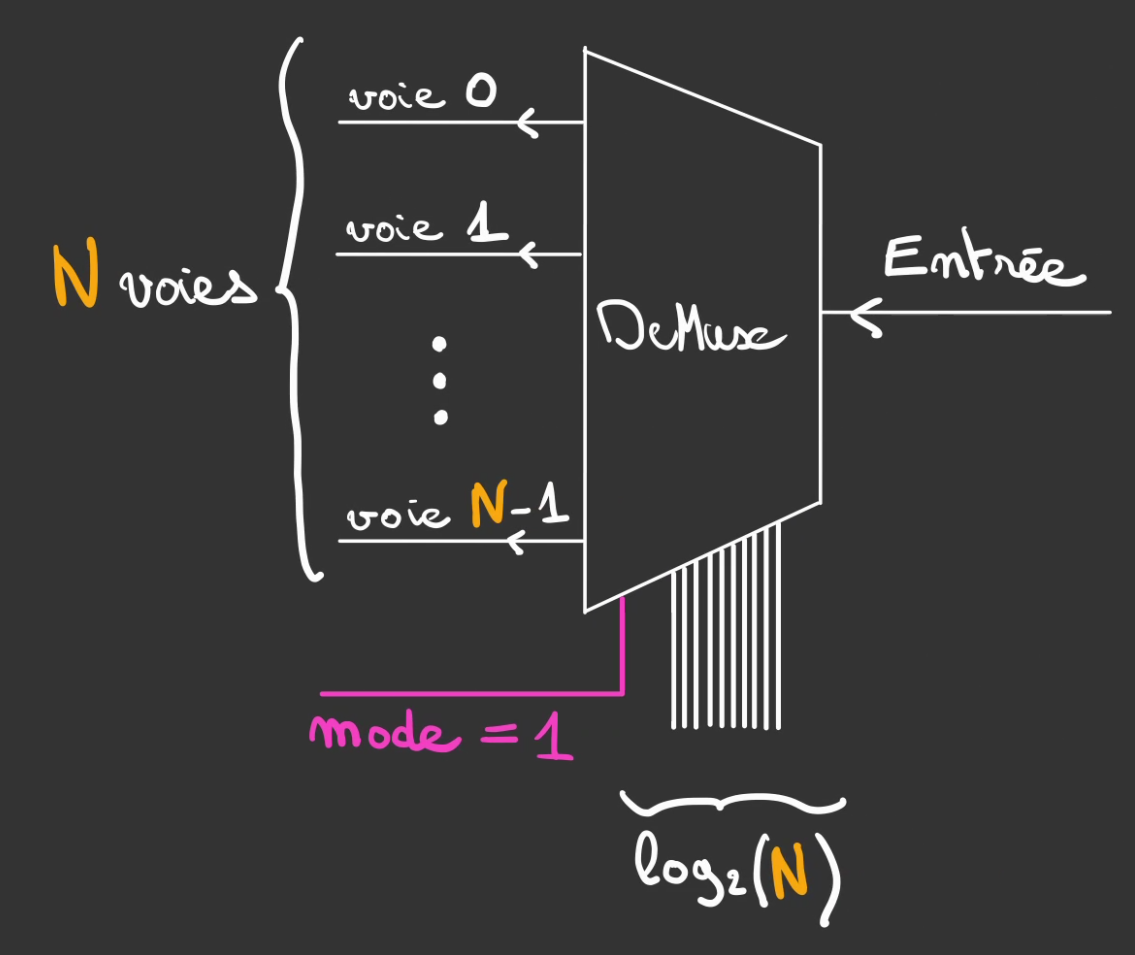

Le demultiplexeur est simplement un multiplexeur monté à l'envers.

On dispose d'une entrée que l'on souhaite recopier sur une voie.

Le mutiplexeur était l'inverse, on avait une multitude de voies que l'on souhaitait recopier sur une sortie unique.

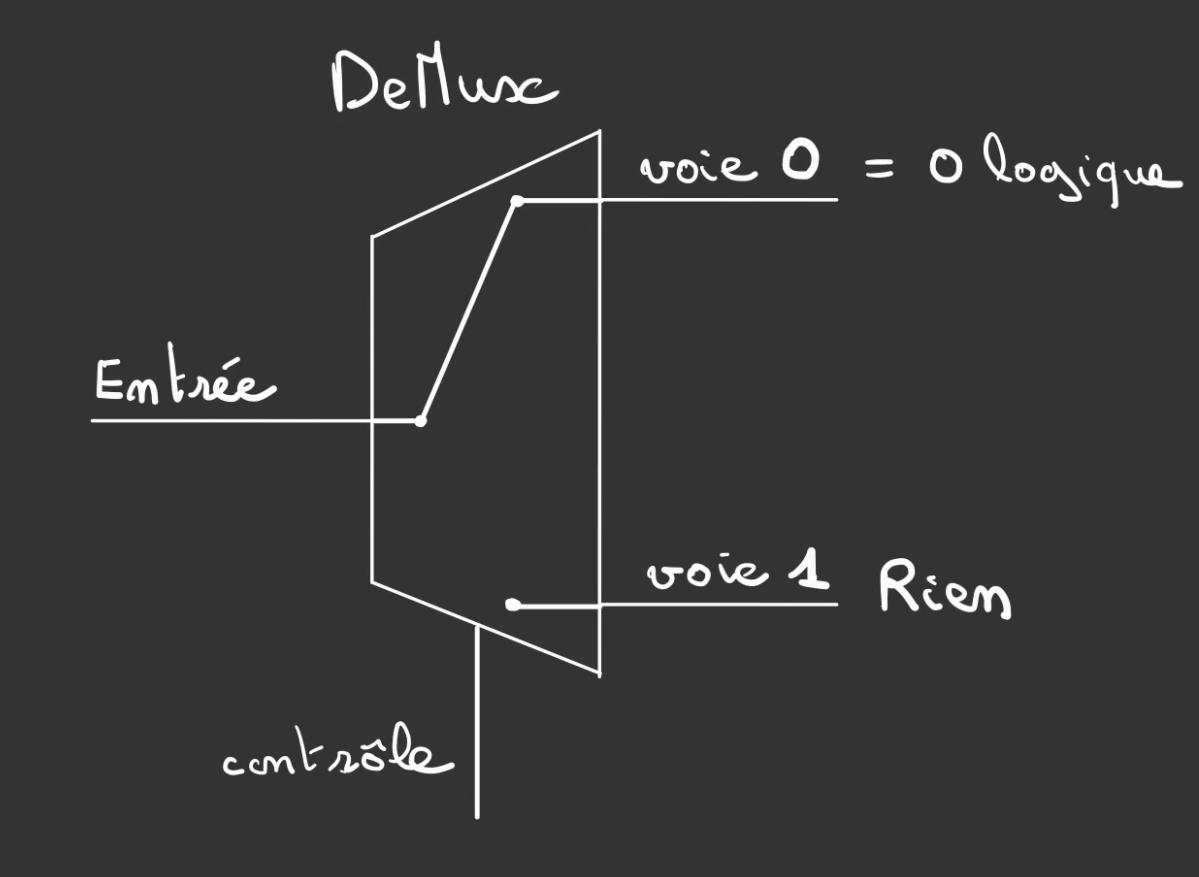

Ici même principe, si le fil de contrôle vaut 0 alors la l'entrée est connectée à la voie 0, la voie 1, est elle laissée complètement dans le vide, l'équivalent d'un fil coupé.

Ce qui fait que si l'entrée vaut 0, la sortie vaudra également 0.

Ceci est la différence fondamentale par rapport au décodeur qui n'était capable que de définir un état haut sur une voie en fonction d'un signal de contrôle.

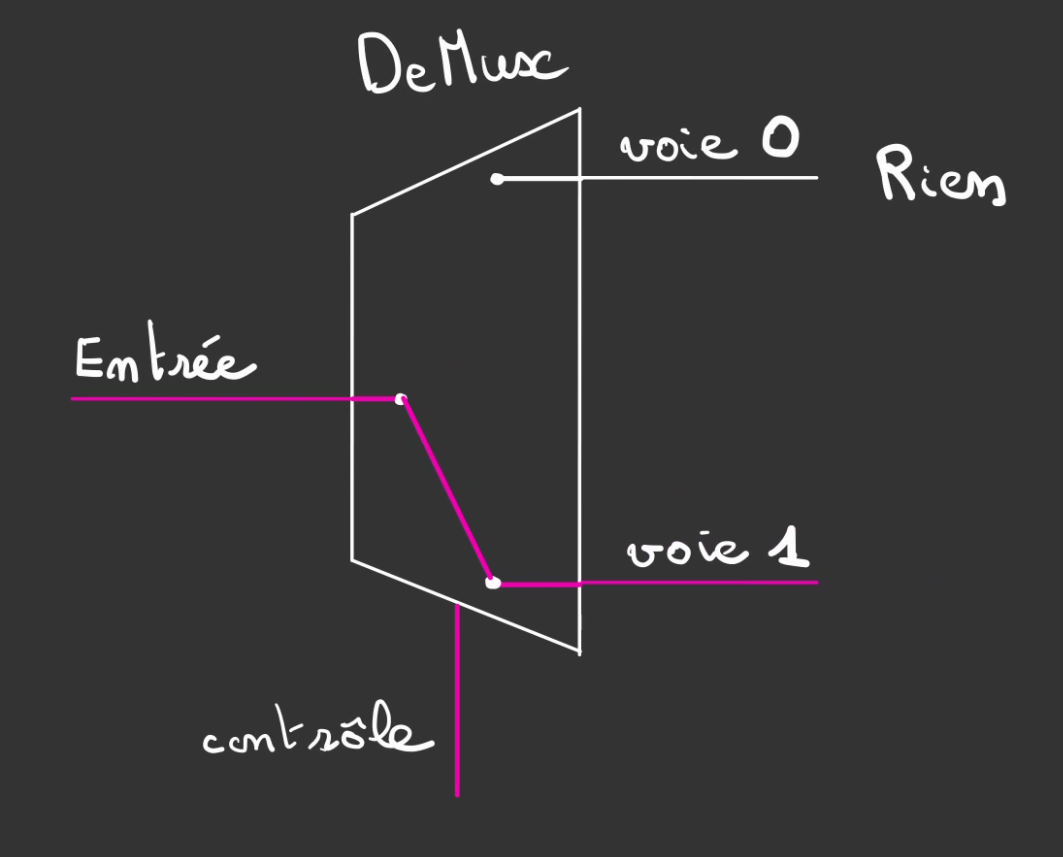

L'aiguillage de l'entrée peut être modifié pour être connecté à la voie 1 en passant le contrôle à 1.

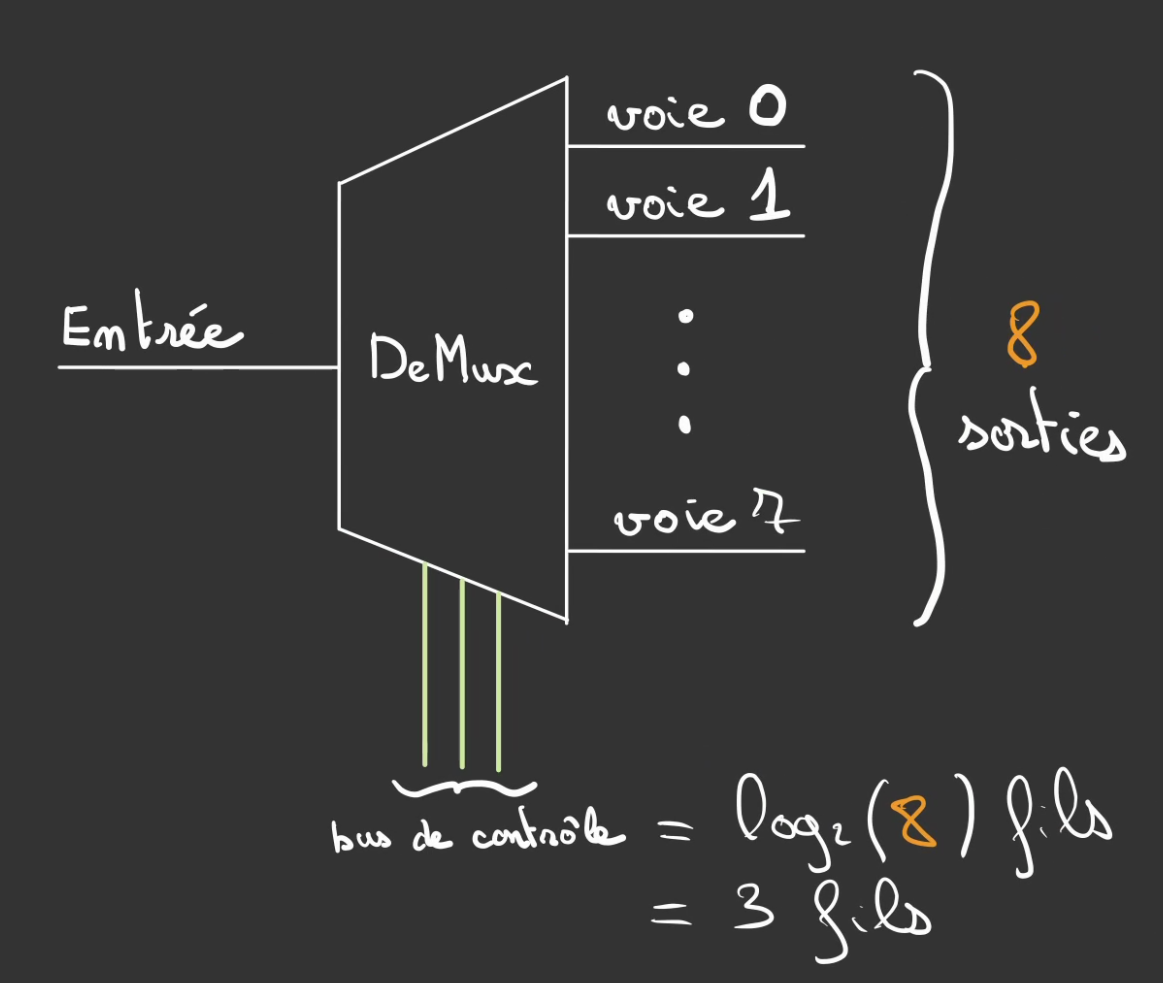

On peut alors augmenter le nombre de voies, ici 8.

Et comme toujours, vous commencez à connaître la chanson, on peut généraliser à N voies. Et par conséquent log2(N) contrôles.

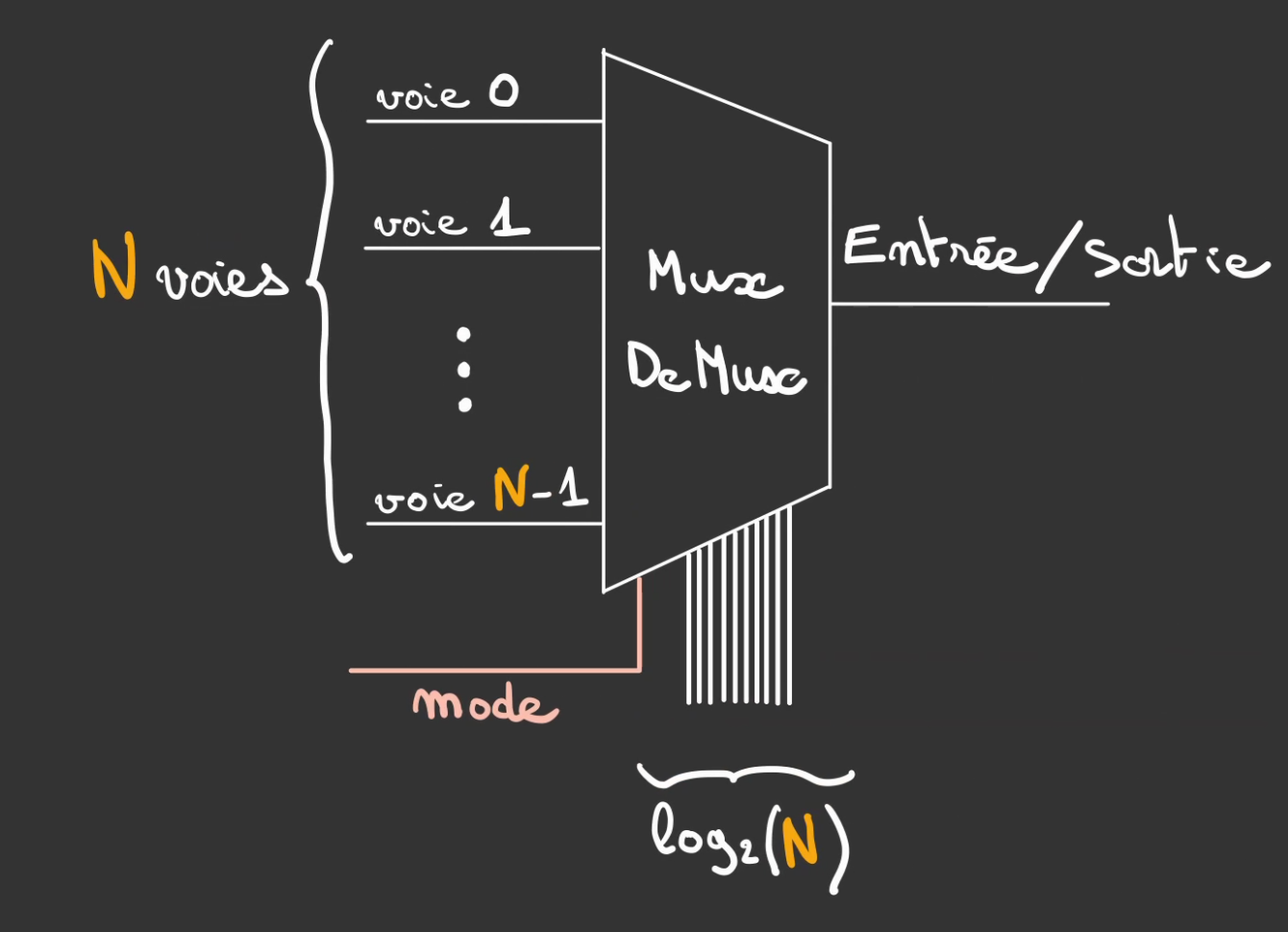

Mux/DeMux

Comme on peut le voir le Multiplexeur et le Démultiplexeur sont très semblables. Ils partagent tout deux les même connexions. Seuls les entrées et les sorties sont inversées.

On va ainsi pouvoir définir un nouveau composant qui se nomme un Mux/DeMux qui possède un fil de contrôle supplémentaire mode.

Dans ce composant hybride, les connexions sont à la fois des entrées et des sorties.

Tout dépend de l'état du fil mode.

Si celui-ci est à l'état 0. Le composant se comporte comme un Multiplexeur.

Les voies sont les entrées et la sortie, et bien la sortie. 😅

Si mode vaut 1 alors la sortie devient l'entrée et les voies les sorties.

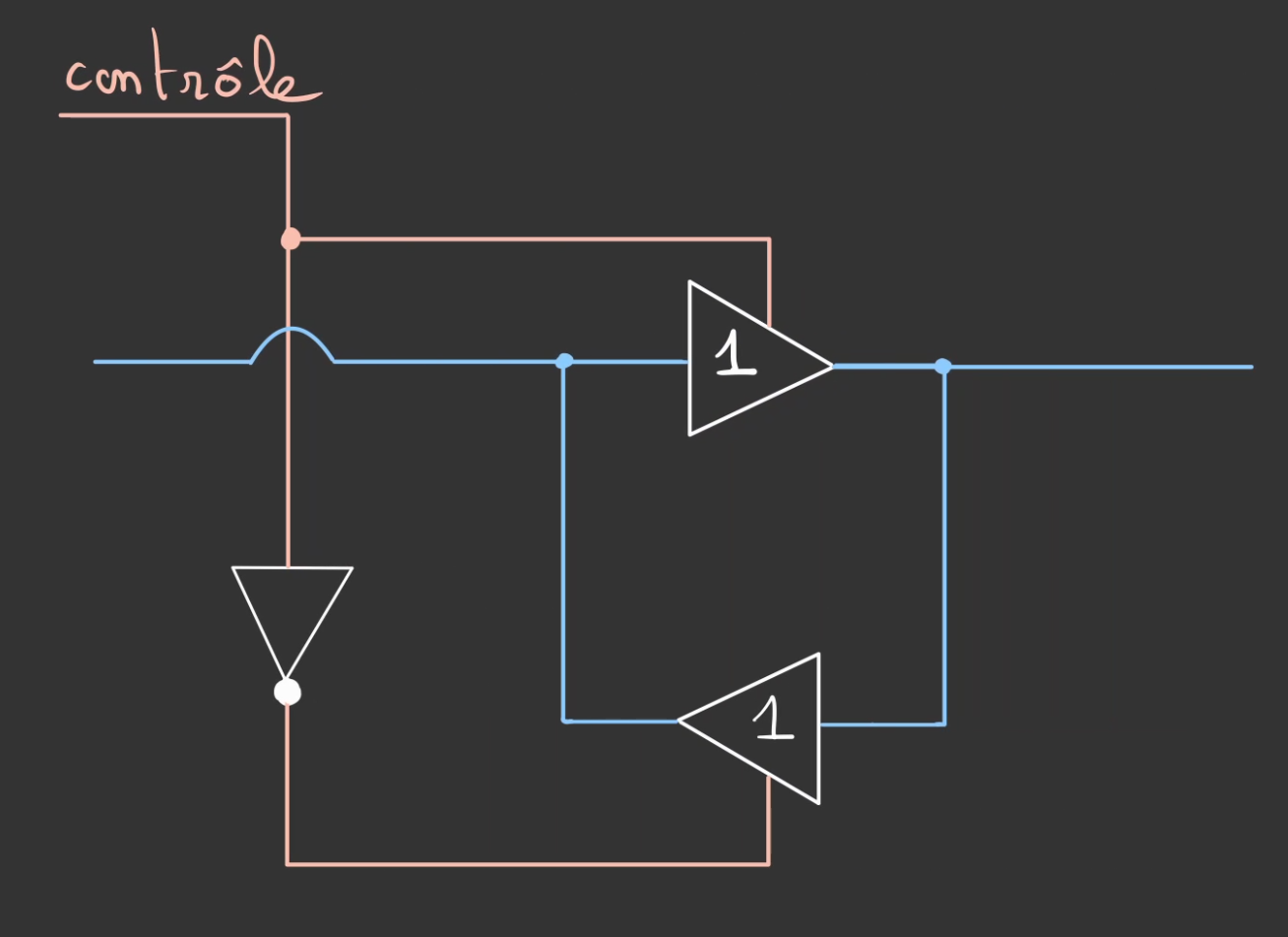

Buffer I/O

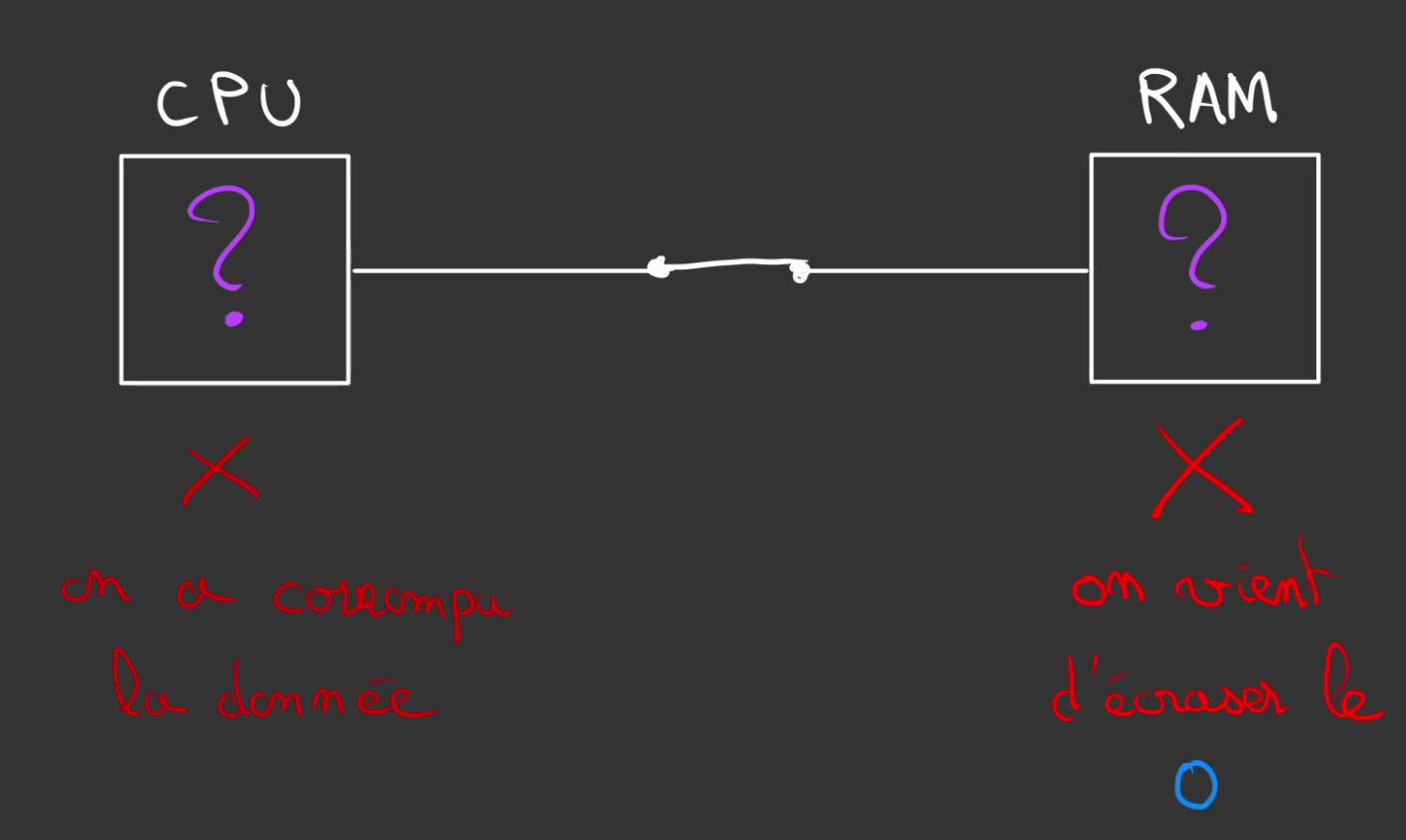

Jusqu'à présent on ne faisait que lire de l'information depuis la mémoire, mais si l'on se met à écrire également de la données.

Comment empêcher que ce qui est contenu dans le CPU n'aille écraser le contenu de la RAM ?

Tant que la cellule n'est pas sélectionnée, pas de souci. Elle est physiquement déconnecter du reste.

Par contre dès que le bus d'adresse sélectionne la cellule, elle devient physiquement relié à l'extérieur et l'extéreur peut très bien être un 1.

Si la valeur était à la base un 0, on peut très bien avoir écrasé la donnée avant d'avoir été capable de la lire.

On se retrouve dans un état indécis, peut-être qu'il y a un 0 ou peut-être un 1, possiblement quelque chose entre les deux.

Le fil allant dans les deux sens, l'inverse est également vrai.

Il nous faut un mécanisme, nous permettant d'isoler notre système lors de la lecture mais aussi de l'écriture.

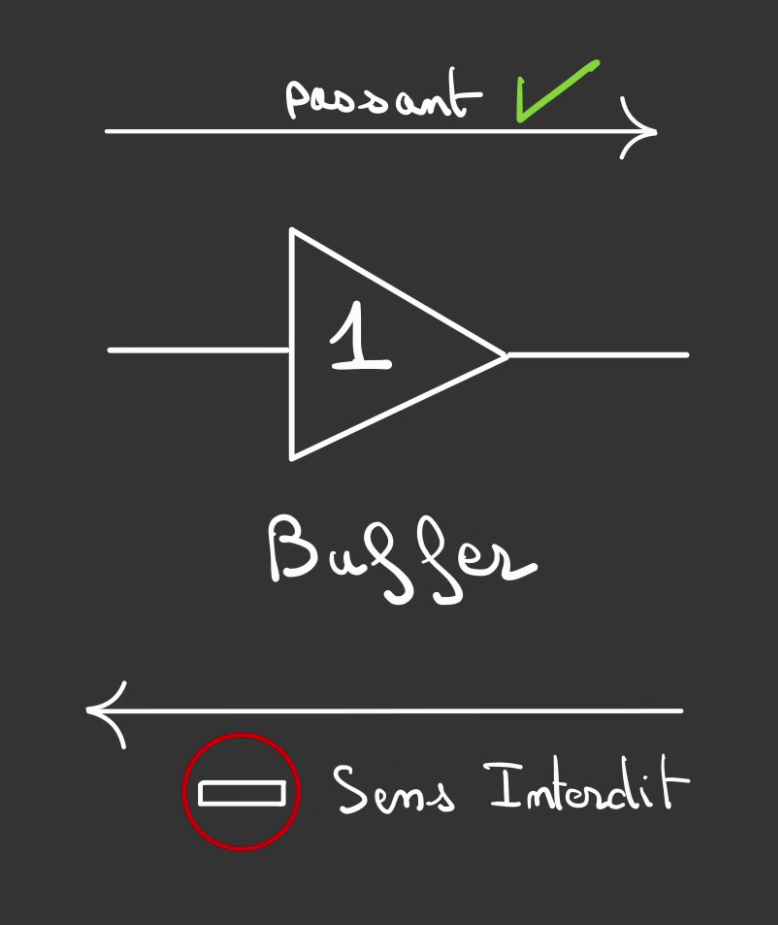

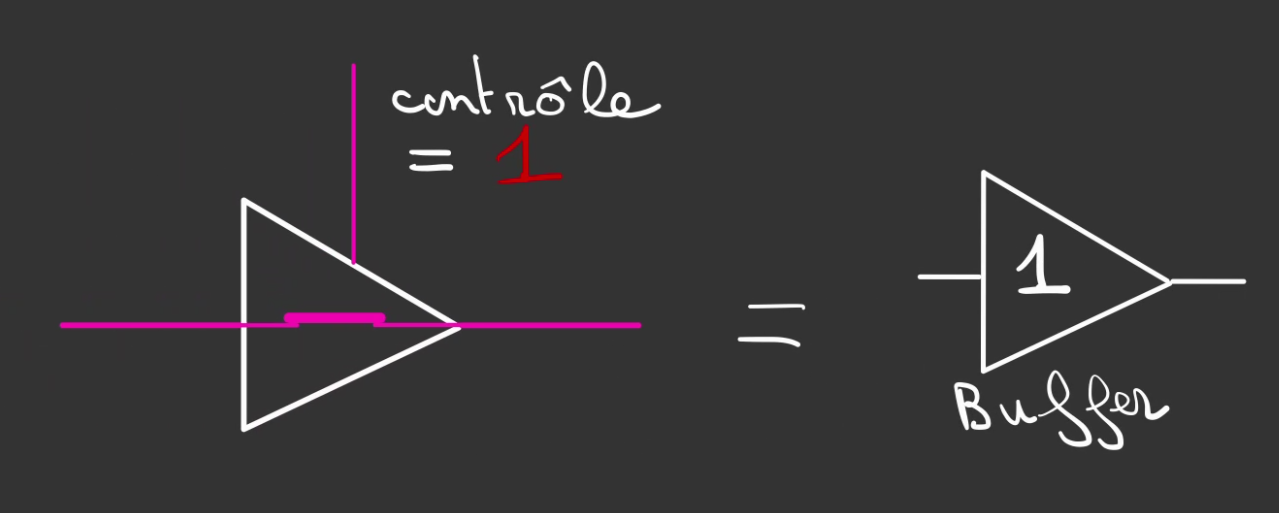

Déjà nous allons avoir besoin d'un système qui n'est passant que dans un seul sens, on nomme ceci un buffer.

On va alors contrôler ce buffer pour le rendre ou non passant.

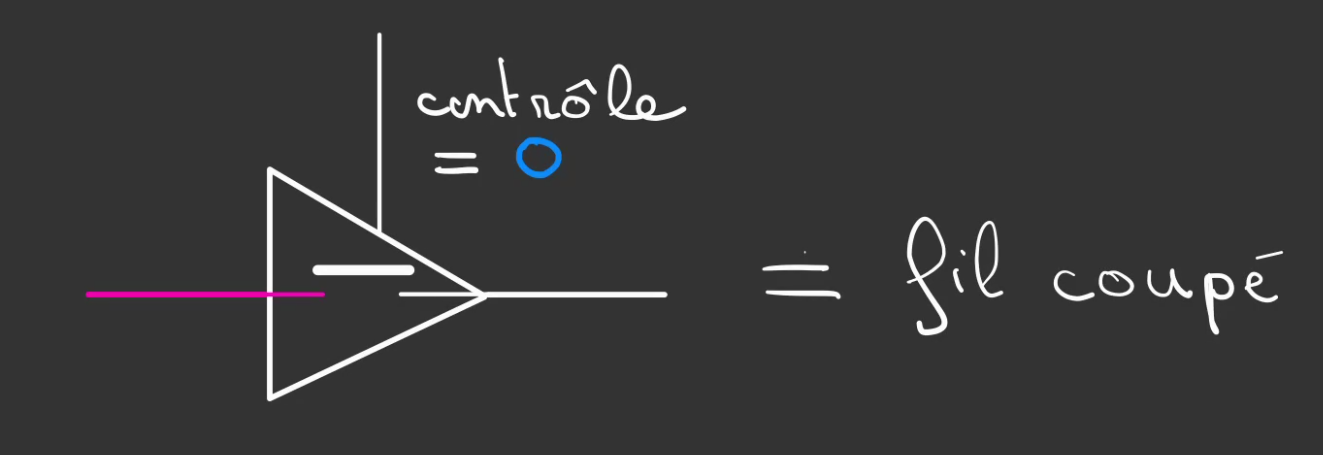

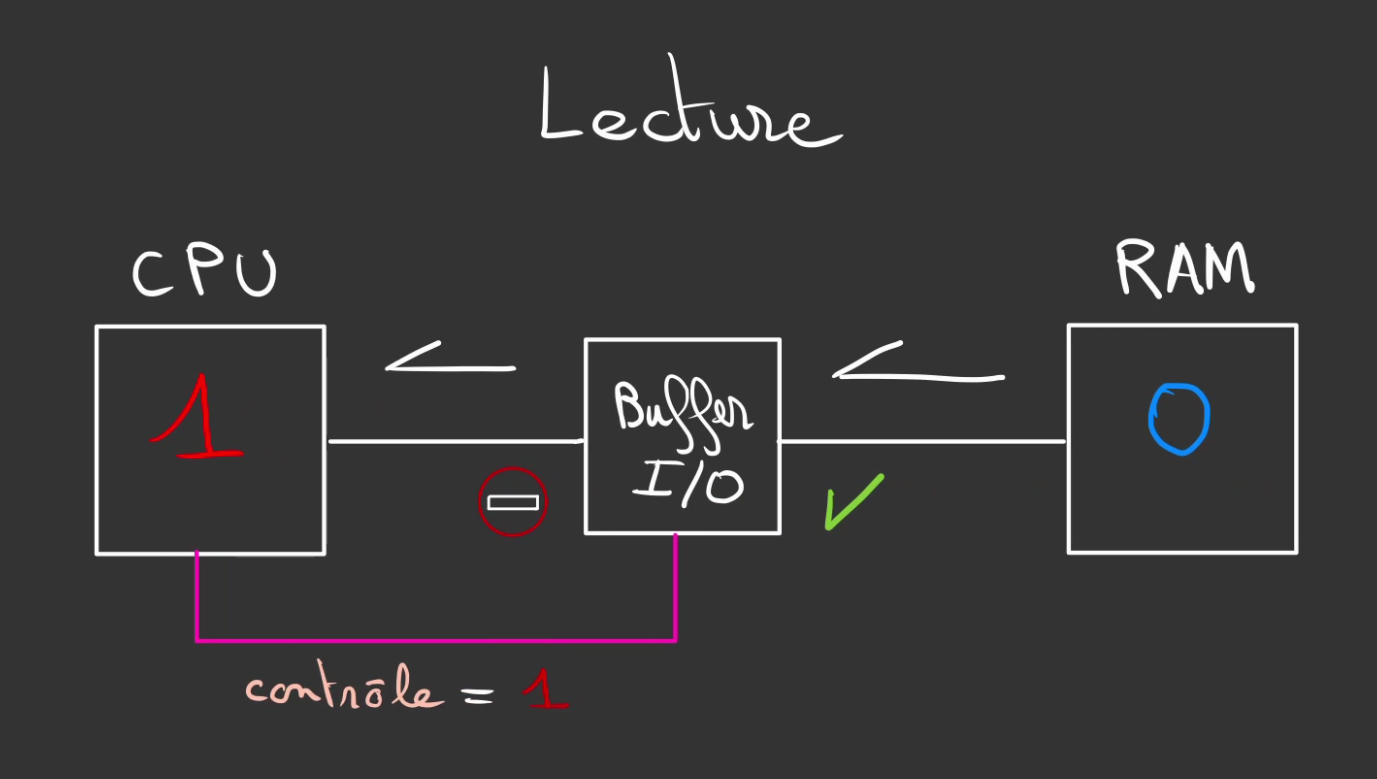

- Si le contrôle vaut

0, le système est bloquant et se comporte comme un fil coupé.

- Si le contrôle vaut

1, le système est passant.

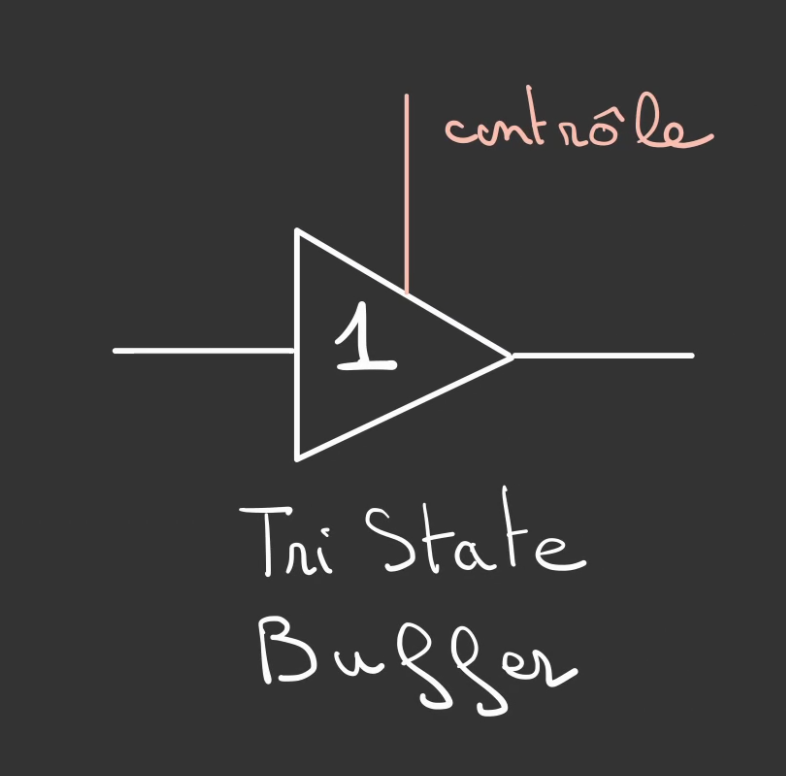

On appelle ça un Tri State Buffer car du point de vue de la sortie on a:

- état 0

- état 1

- état fil coupé

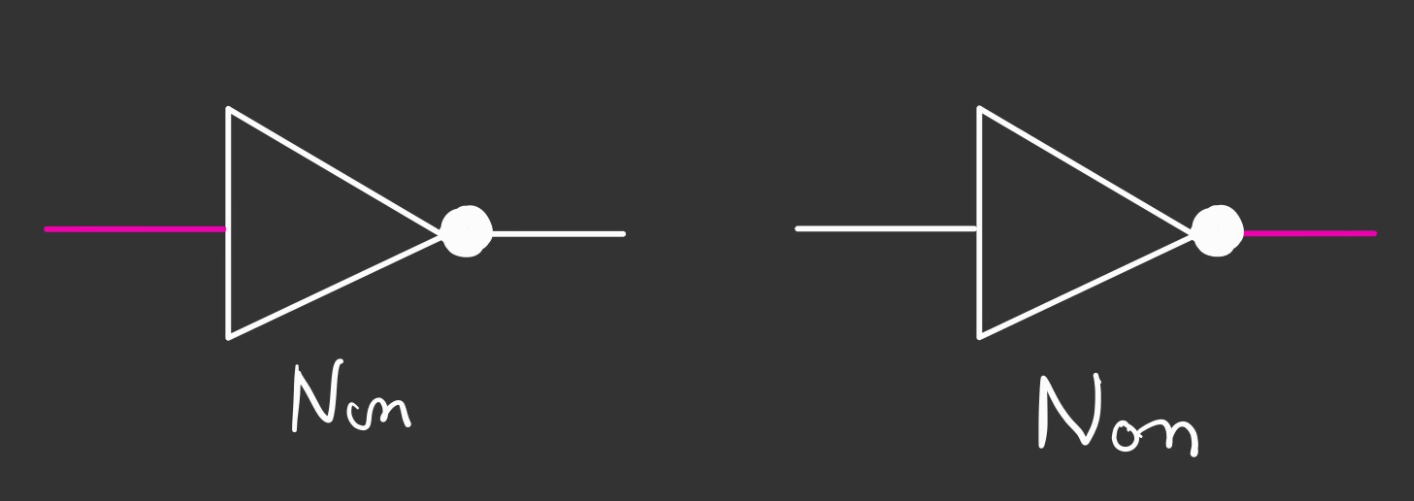

On définit alors un autre composant qui va permettre de faire l'inverse. On nomme ceci une porte NON.

Si l'entrée vaut 1 alors la sortie vaut 0 et inversement.

L'idée est d'avoir un système symétrique.

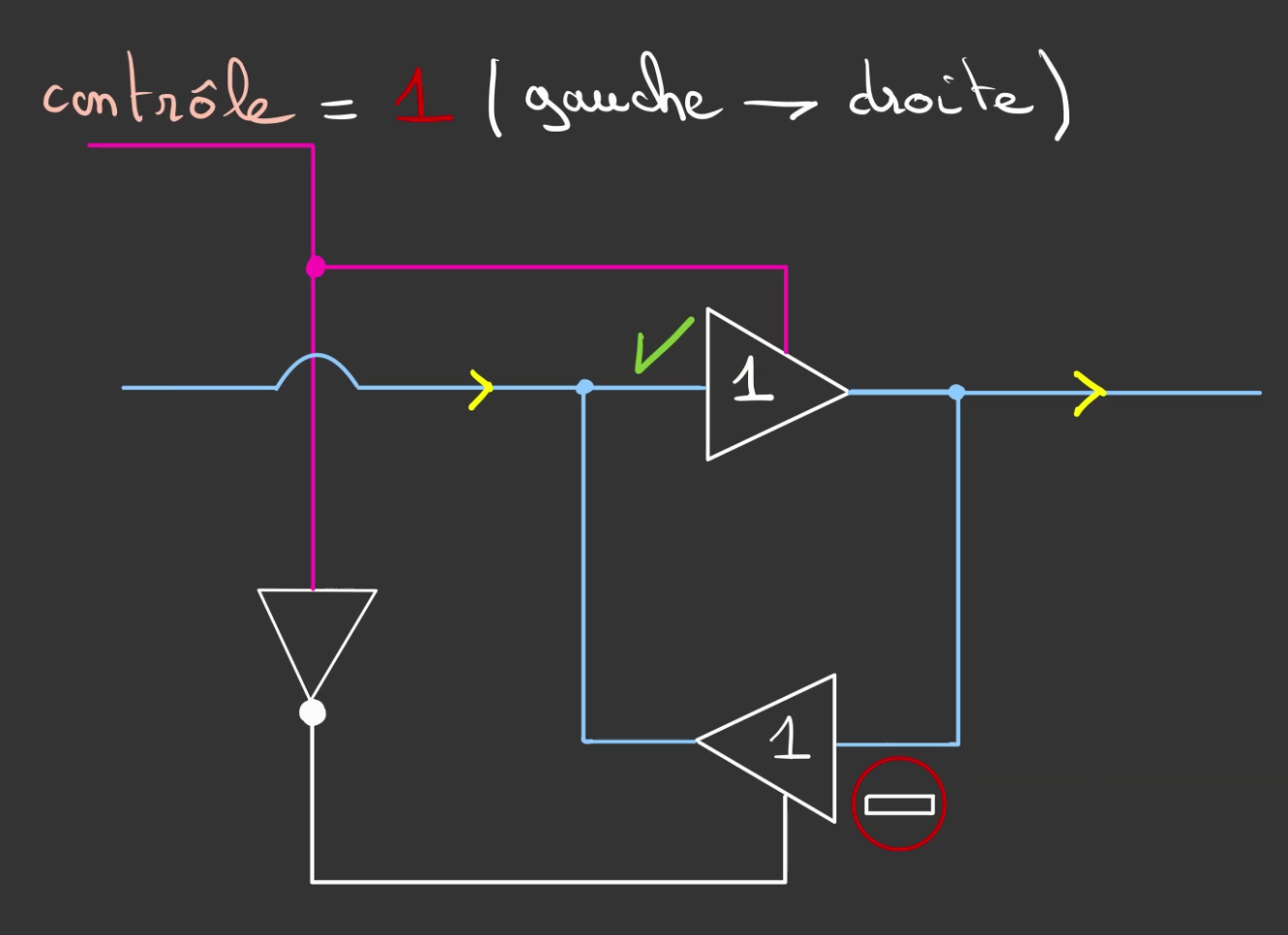

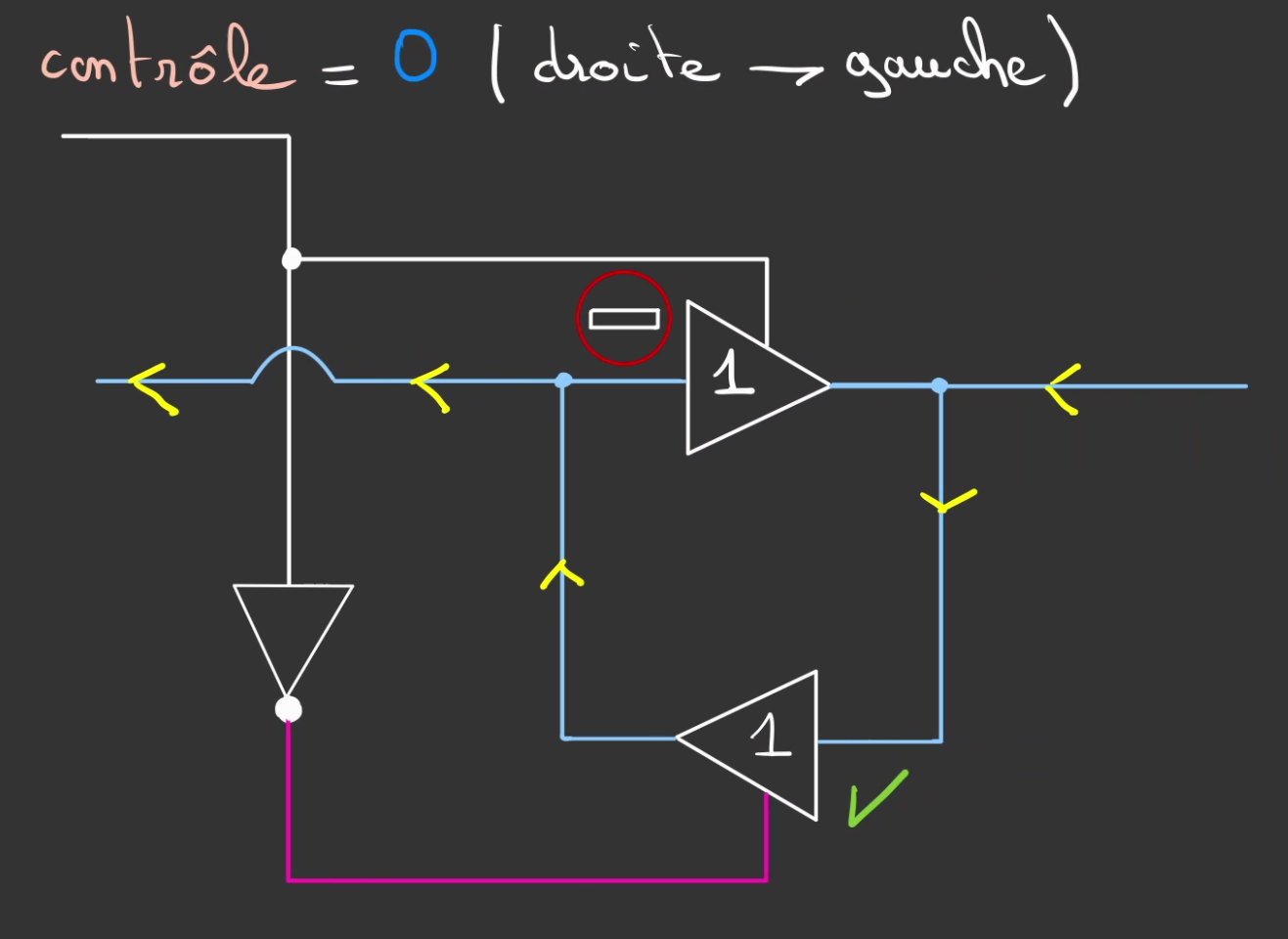

On va alors agencé tête bêche nos deux tri state buffer, connecté l'entré de l'un à la sortie de gauche et connecter l'entrée de l'autre à la sortie de droite. Que l'on contrôle simultanément avec un même contrôle. On inverse le signal sur l'autre buffer.

Ce signal peut avoir deux valeurs:

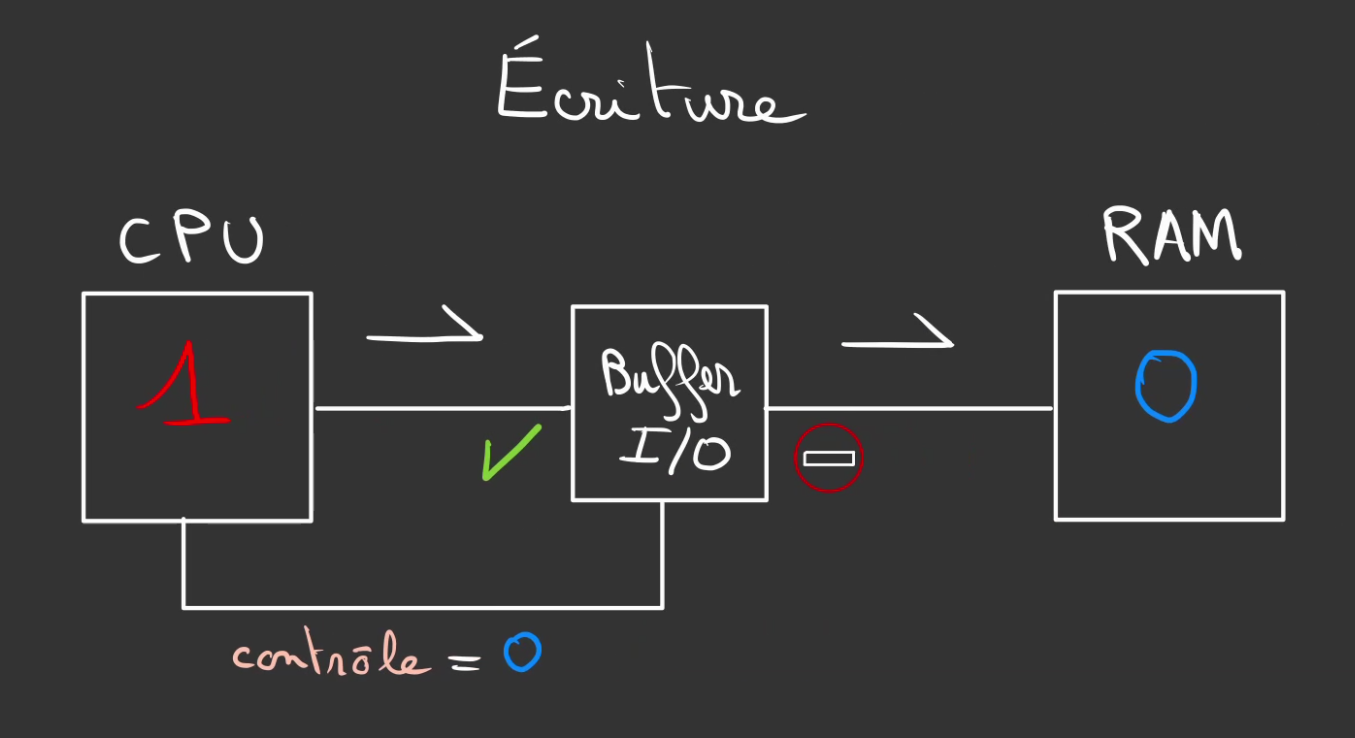

-Si le signal est à l'état 1 les données transitent de la gauche vers la droite.

-Si le signal est à l'état 0 les données transitent de la gauche vers la droite.

On peut alors en faire un composant à 2 connexions de données et 1 fil de contrôle.

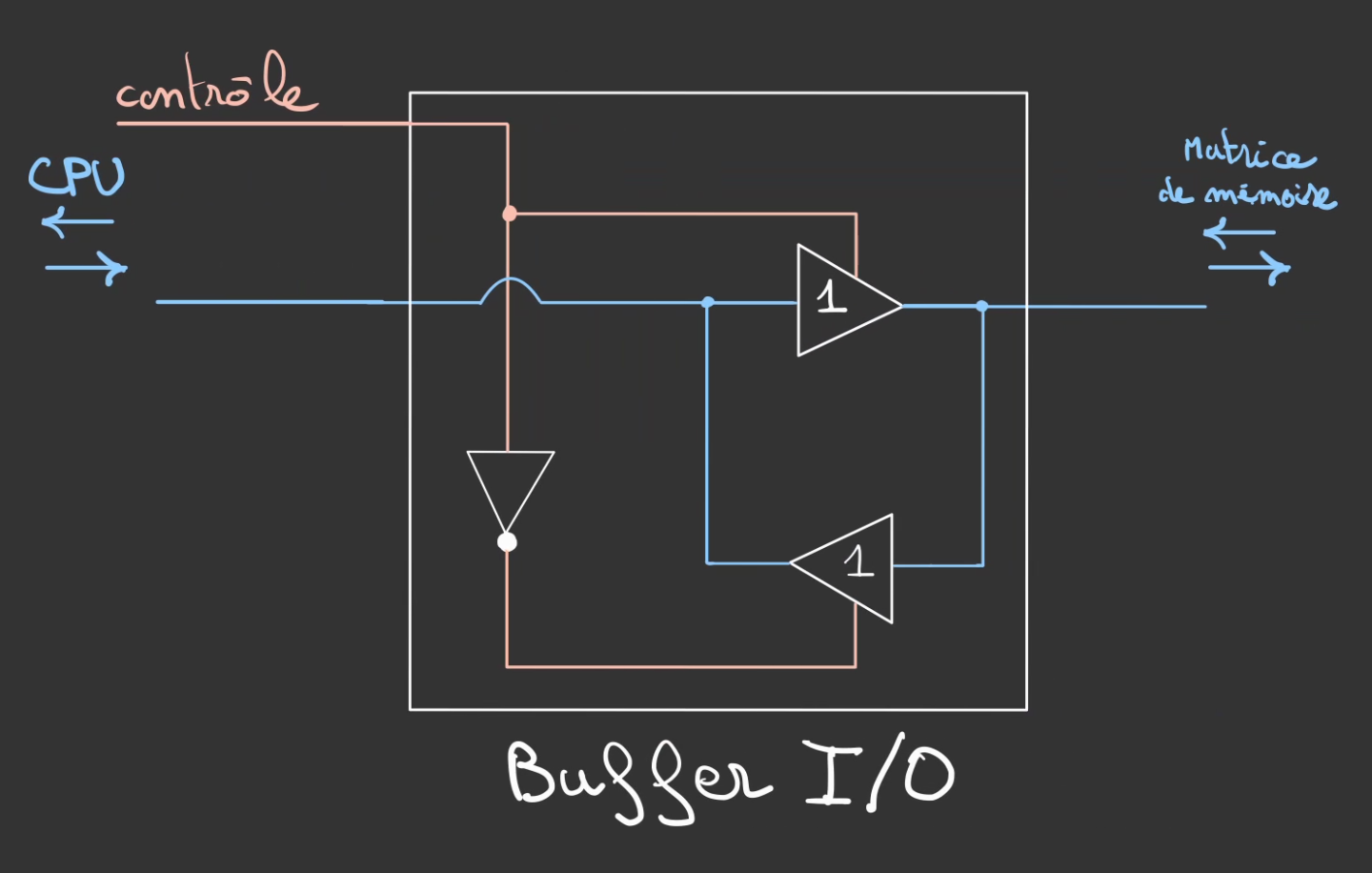

Ce composant se nomme un Buffer I/O.

Que l'on peut alors intercalé dans notre système de tout à l'heure.

On vient également brancher le CPU au contrôle, ainsi c'est lui qui devient moteur de la désicion du flux de données

En Lecture

Ou en Ecriture

Ce choix est purement arbitraire, le Buffer I/O pourrait-être monté dans le sens inverse.

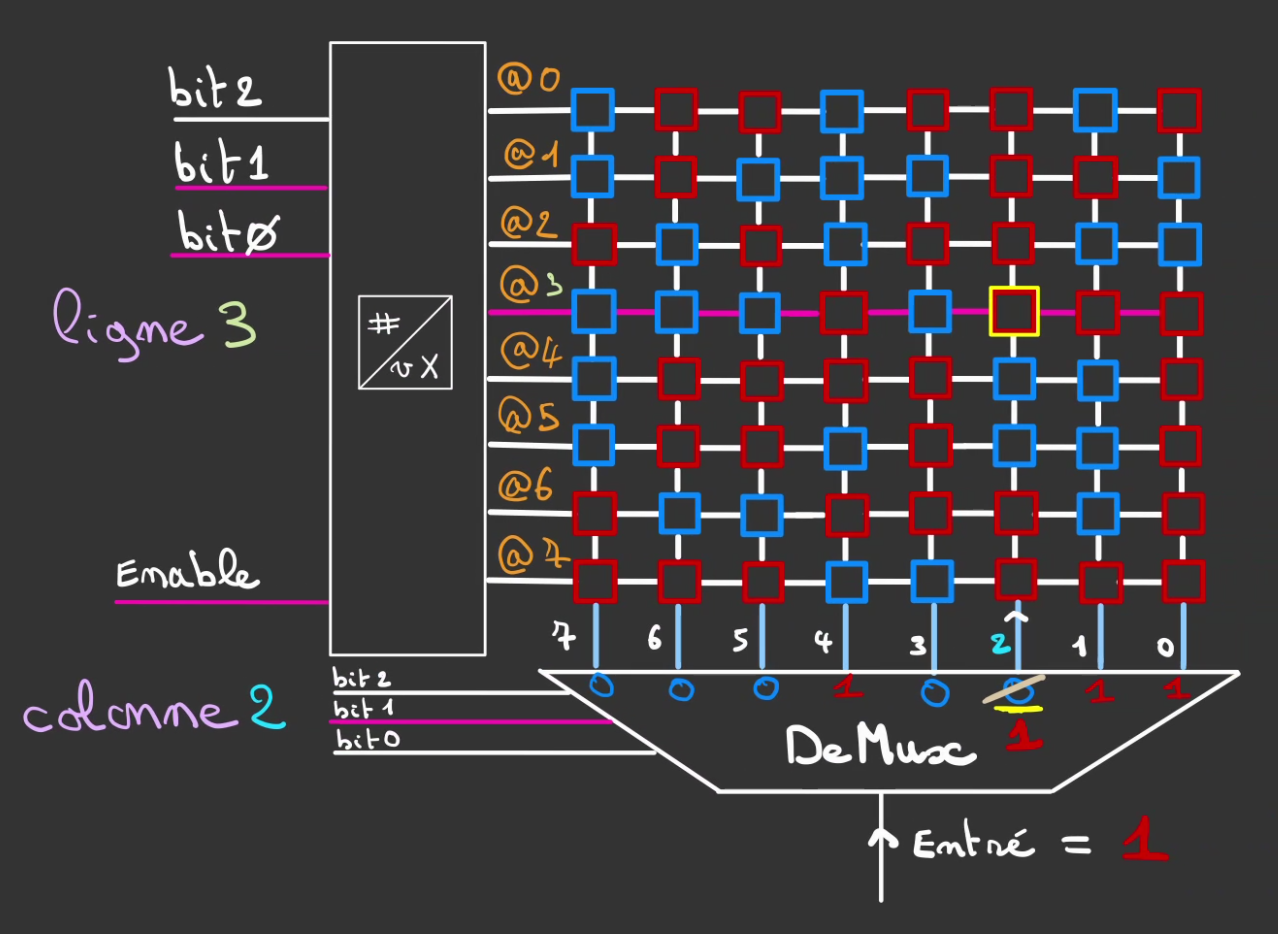

Modifier les matrices

Nous avons désormais tous les outils pour travailler.

Nous allons temporairement remplacer le multiplexeur par un démultiplexeur.

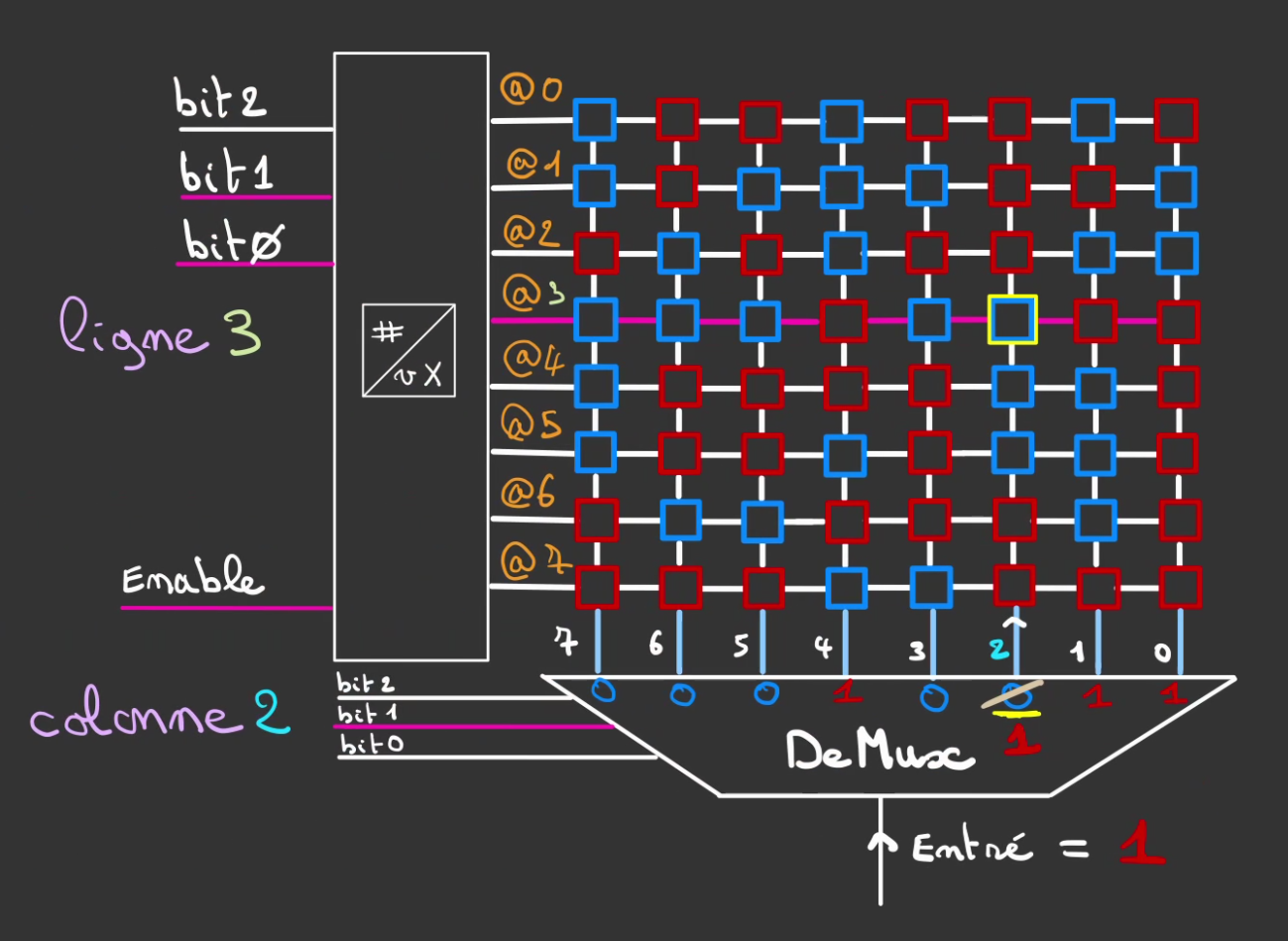

Imaginons que l'on souhaite modifier la case à l'adresse 011010.

Soit colonne 2 et ligne 3.

Sa valeur est actuellement de 0. On désire y inscrire 1.

Le démultiplexeur est réglé pour rediriger l'entrée sur la voie 2.

On applique un 1 sur l'entrée.

Ce qui a pour effet de modifier la cellule aux coordonnées (2, 3) mais laisse inchangées les autres.

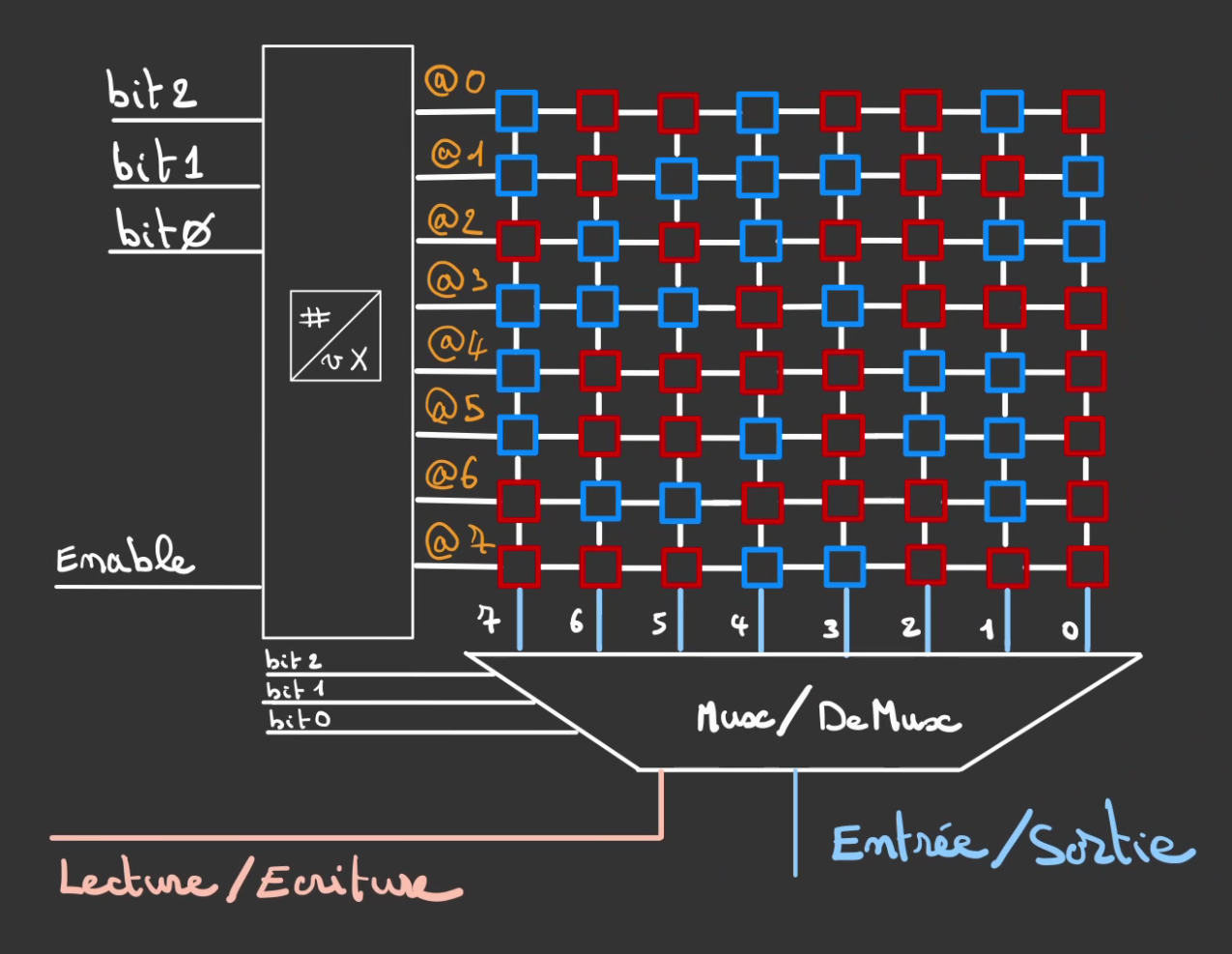

Comme nous désirons à la fois écrire et lire dans la matrice.

On utilise notre Mux/DeMux.

On ajoute également un fil supplémentaire pour réaliser le changement de mode du Mux/DeMux.

On rajoute également le Buffer I/O que l'on contrôle avec le même signal que le Mux/DeMux.

Ce qui permet de ne pas modifier par inadvertance une case mémoire.

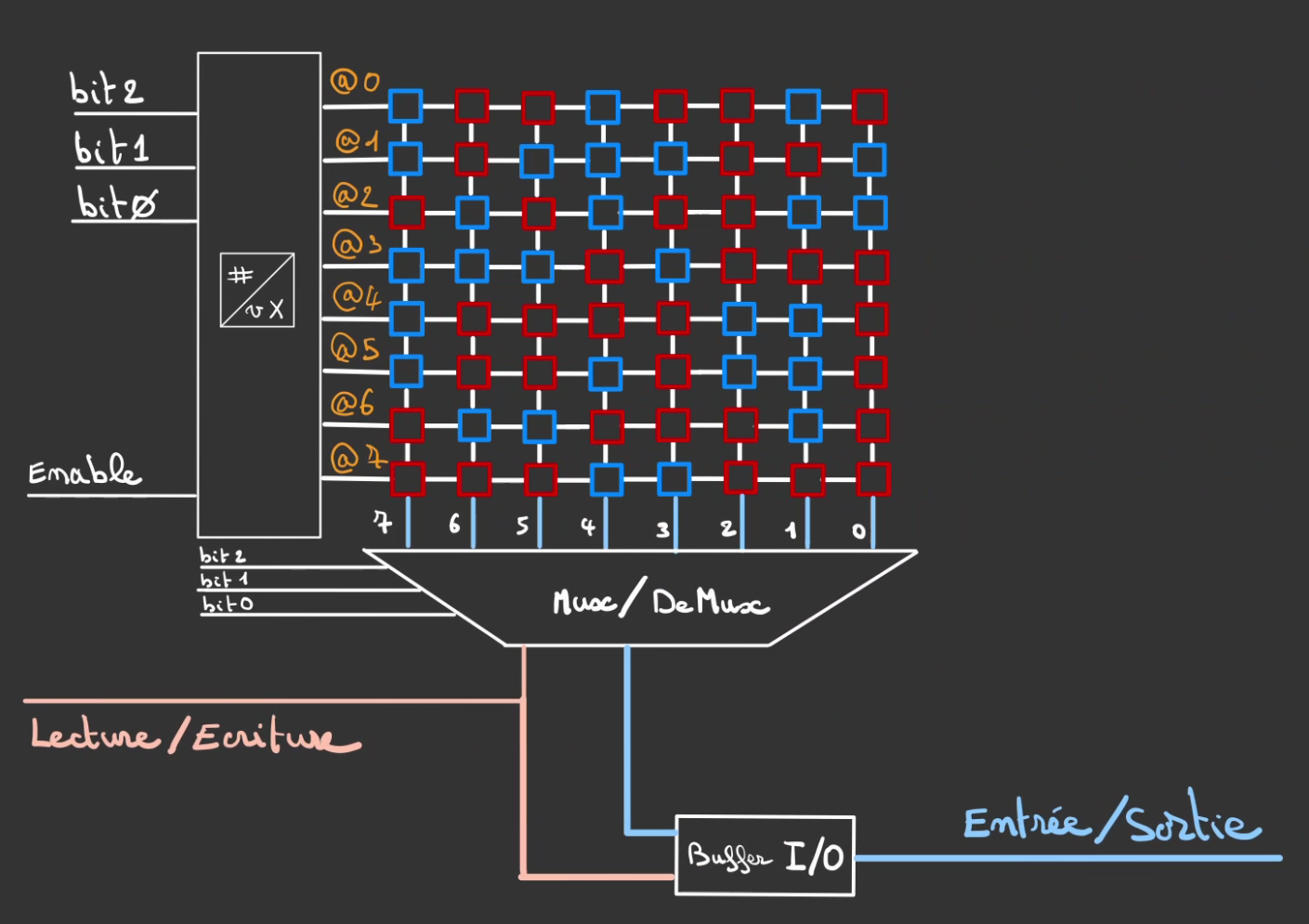

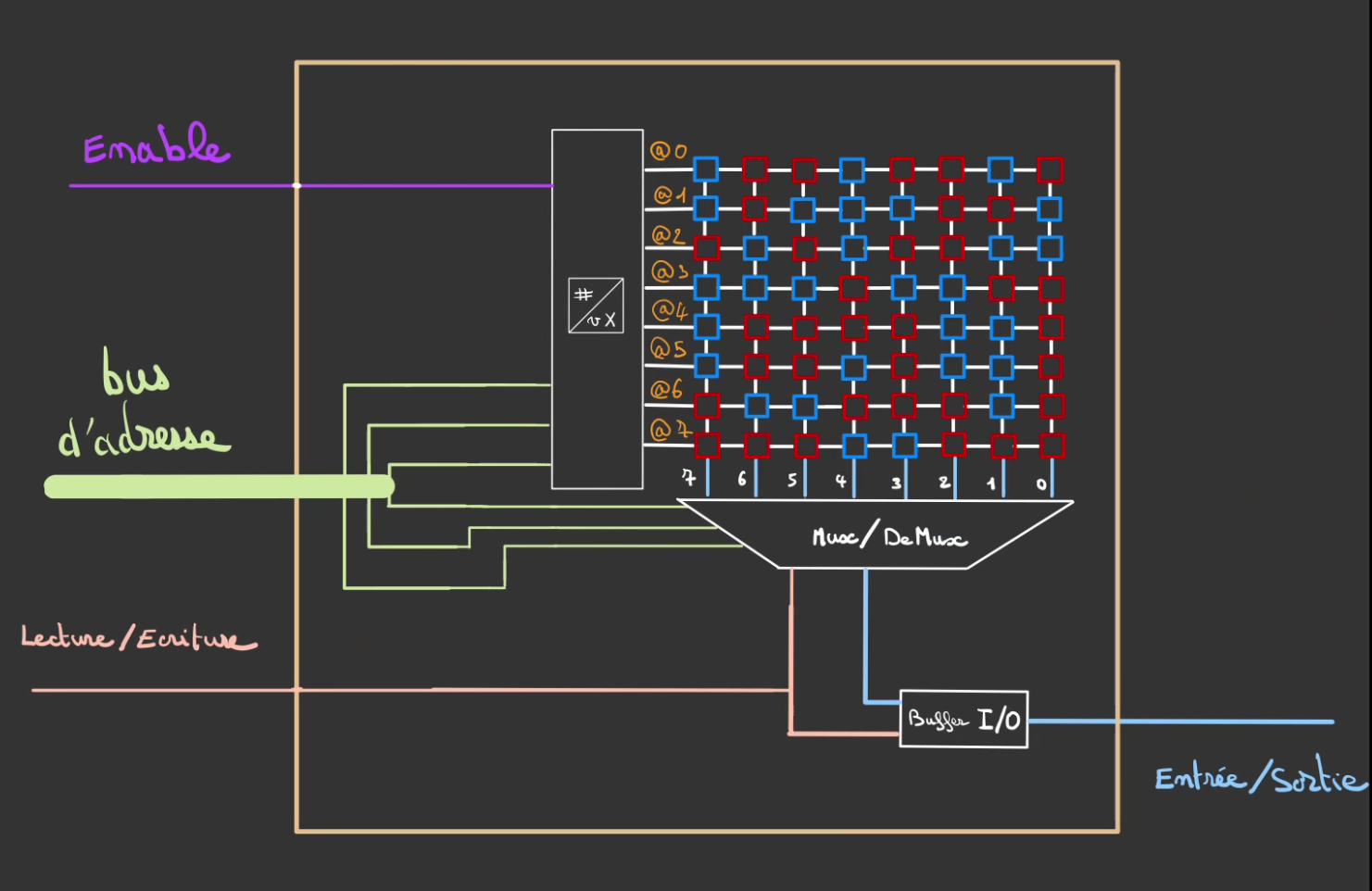

On peut alors faire un composant intégré de ce système.

On verra dans la suite des méthode pour optimiser le nombre d'éléments nécessaires.

On en reviens alors à l'organisation précédente mais avec désormais la possibilité de lire et d'écrire des mots de 64bits.

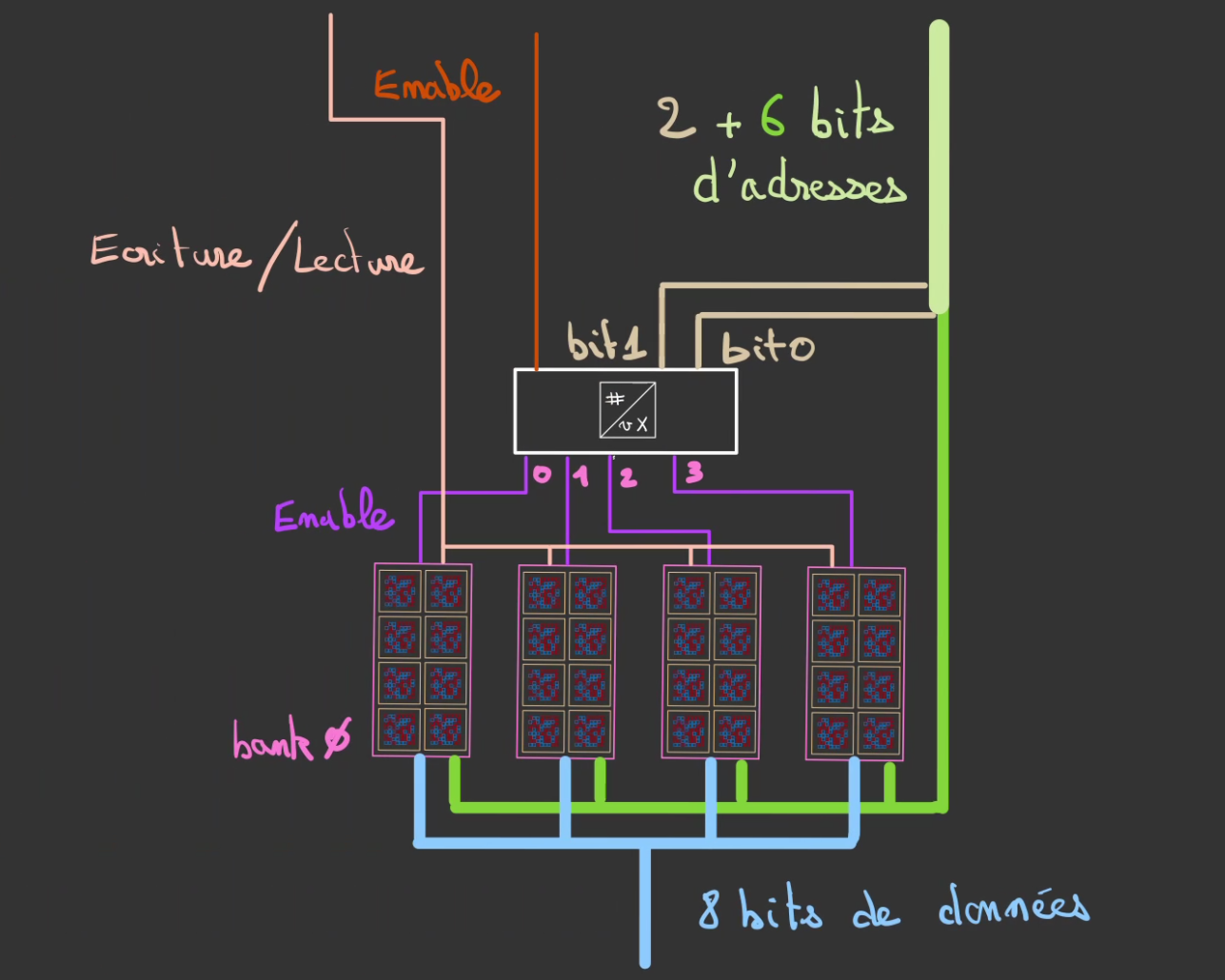

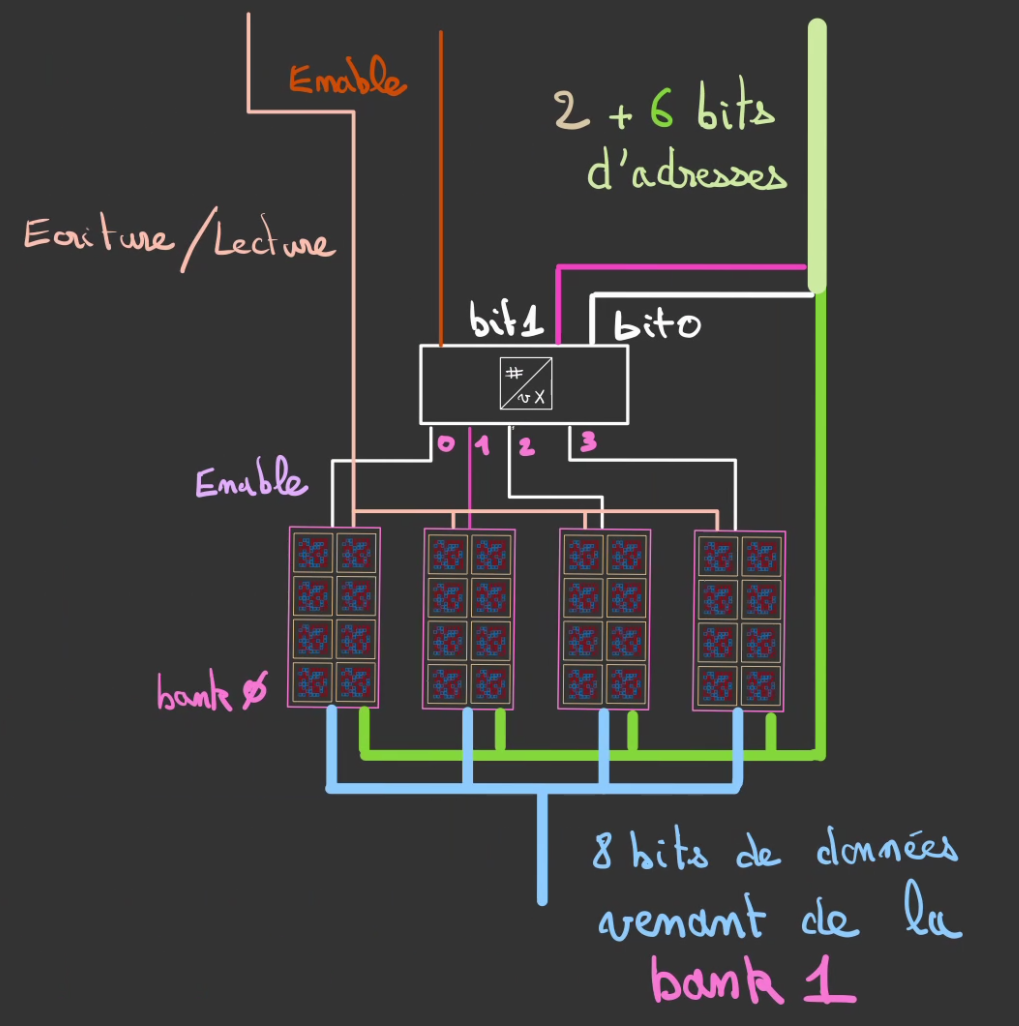

Rank

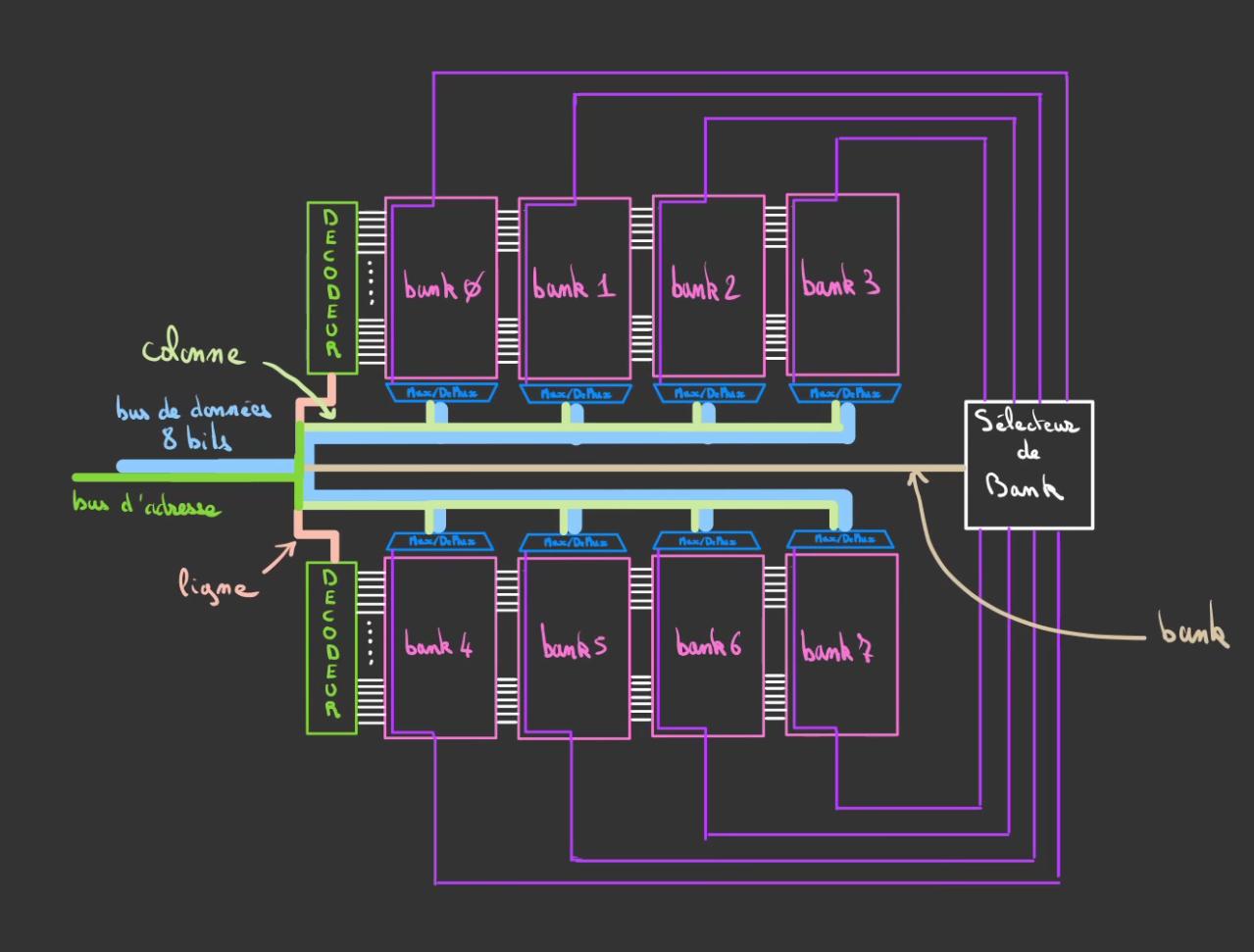

Il est alors possible de subdiviser nos banks en des banks plus petite. Pour cela nous allons utiliser la même astuce que toujours: réserver une partie des fils du bus d'adresse pour un usage différents.

Ici cet usage va être de sélectionne la bank qui possède le bon octet.

Pour cela, on utilise un décodeur qui vient selectionner la bank en fonction de l'adressage que l'on lui fourni.

Si par exemple on souhaite sélectionner un octet situé dans la bank 1, on va alors activer le bit 1 et laisser le bit 0.

Ce qui va activer le signal Enable de la bank 1 et ainsi permettre le décodage de l'adresse de l'octet voulu.

Ce qui permet un adressage non plus en 2 dimensions mais en 3 !

Chaque bank contient un certain nombre d'octets différents.

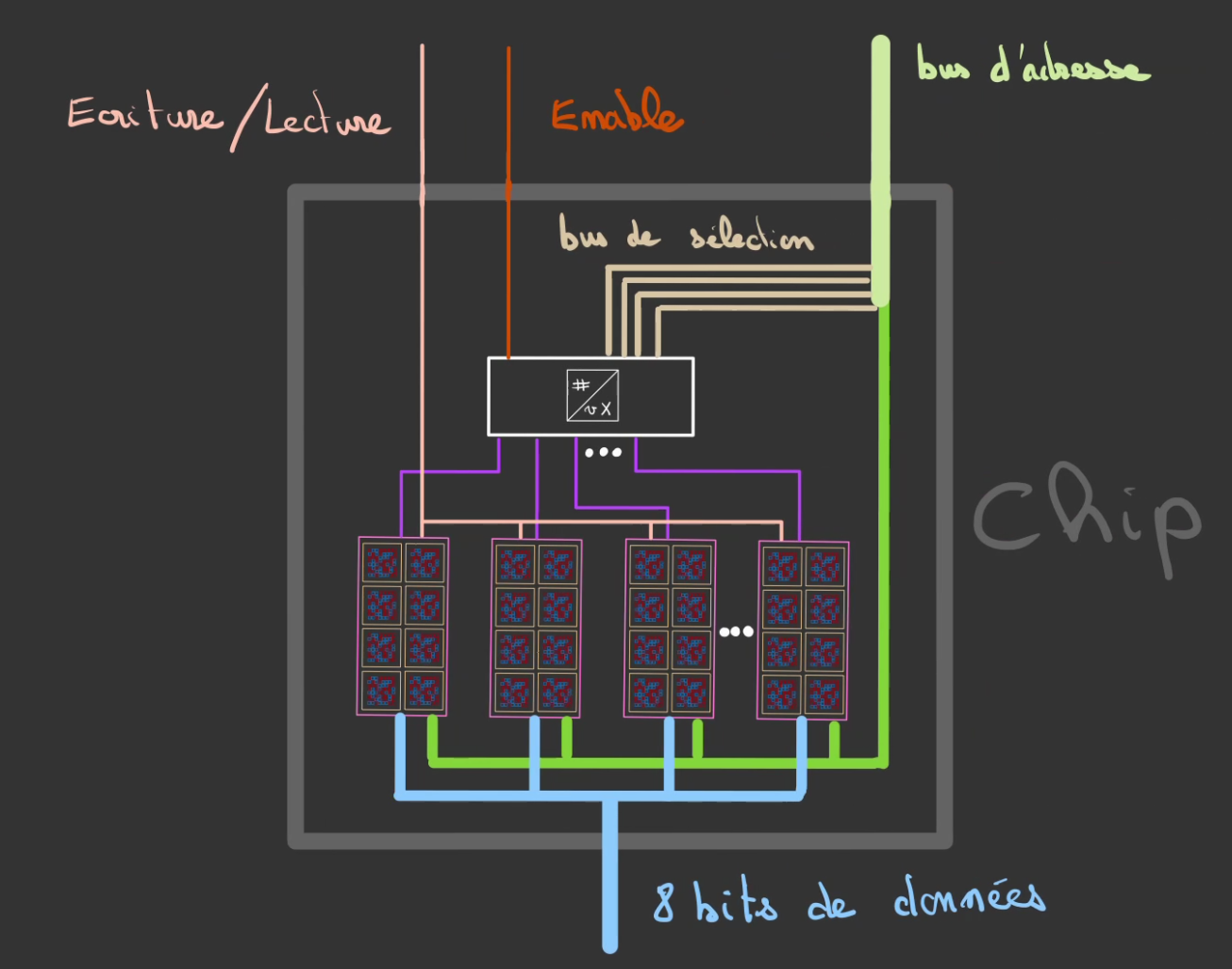

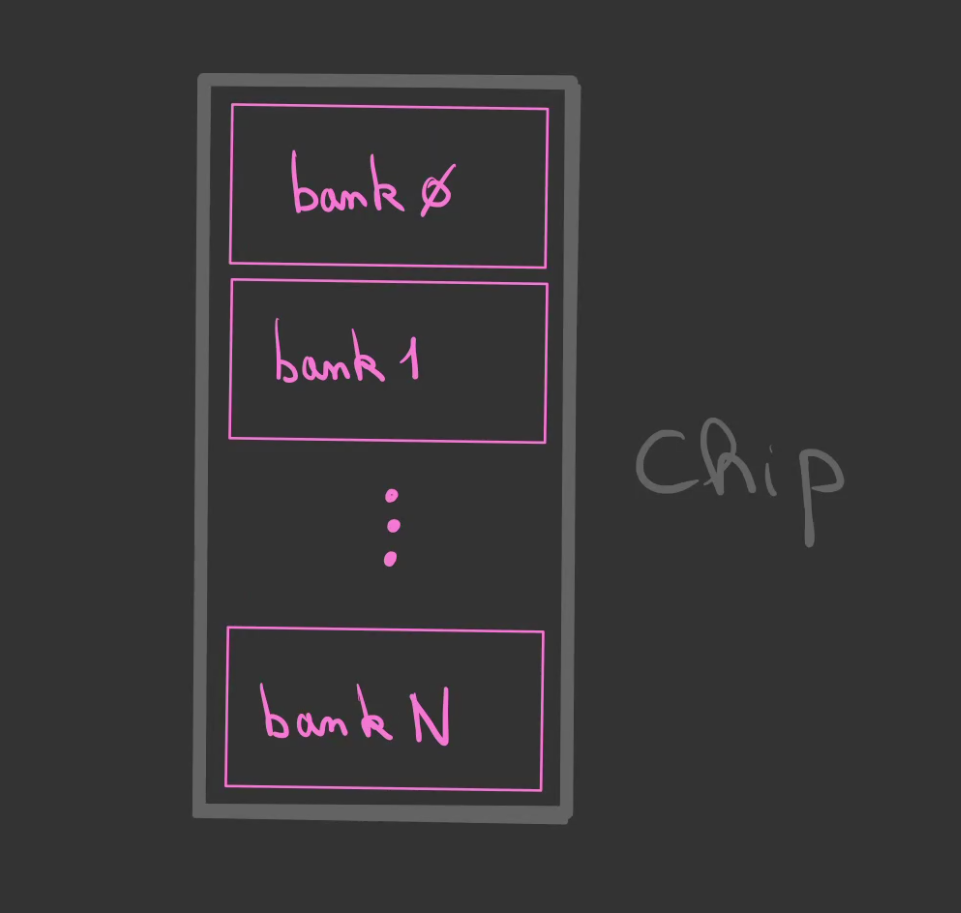

On peut alors en faire un composant que l'on appelle une puce ou Chip.

Qui peut se symboliser par une version simplifiée.

On agence chacun de nos chips comme nous l'avions fait avec les banks, chaque chip représentant un octet. Il nous en faut également 8 pour atteindre les 64 bits.

Et là ça devient fou et c'est le but de tout ce qu'on vient de voir.

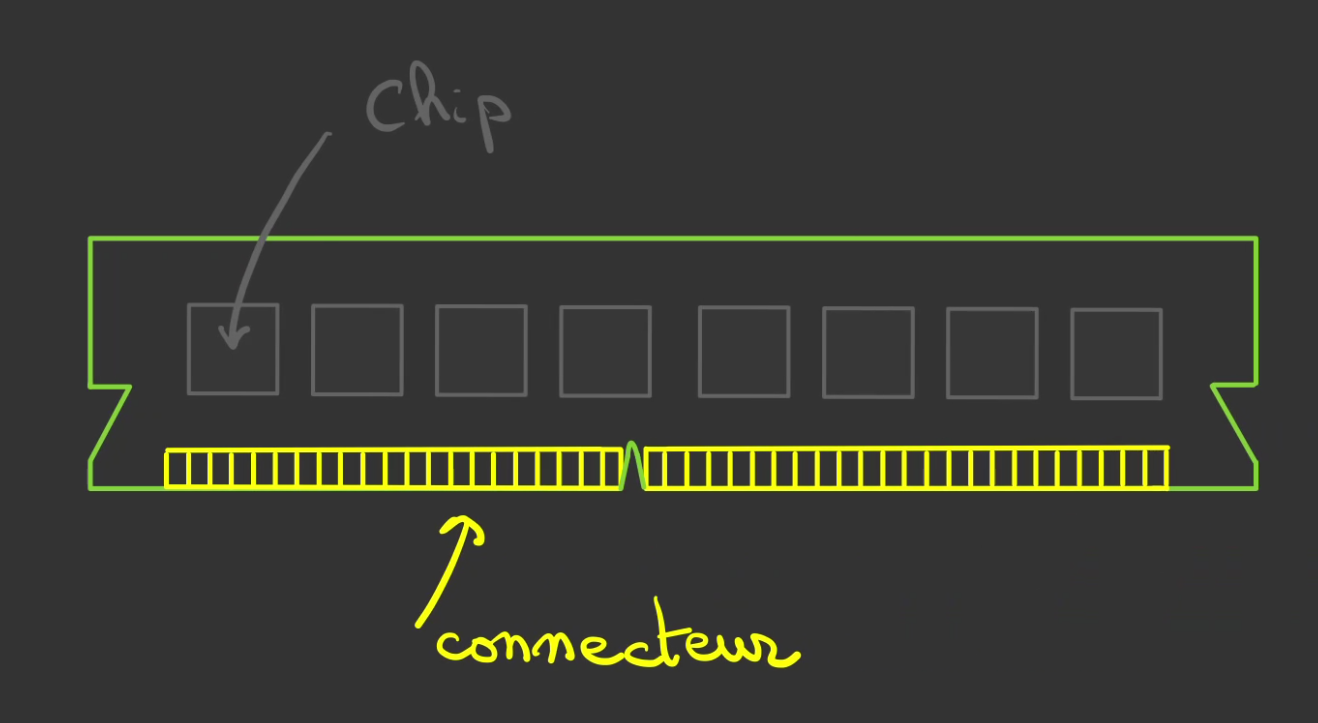

Les 8 rectangles noirs sur la barette de RAM sont les fameux chips !

Lorsque j'ai vu ça, ça m'a donné envie d'écrire cet article mais surtout de comprendre le comment de ce bloc noir. 😁

Optimisation

Maintenant que l'on a en quelque sorte le schéma de principe d'une barette de RAM. Nous allons pouvoir opérer quelques optimisation.

D'une part en matière de nombre de composants utilisés, d'autre part en terme de place prise en mm2.

L'idée restant de maximiser le stockage et de minimiser le nombre de composants nécessaires.

Souvenez vous une bank est composé d'une série 8 matrice posédant chacune leur décodeur de ligne et un multiplexeur.

Et bien il est possible de simplifier cela en permettant de au multiplexeur de manipuler des groupe de 8 cases.

Ainsi lorsque l'on sélectionne une case dans la matrice, c'est en fait 8 cases qui sont sélectionnées simultannément.

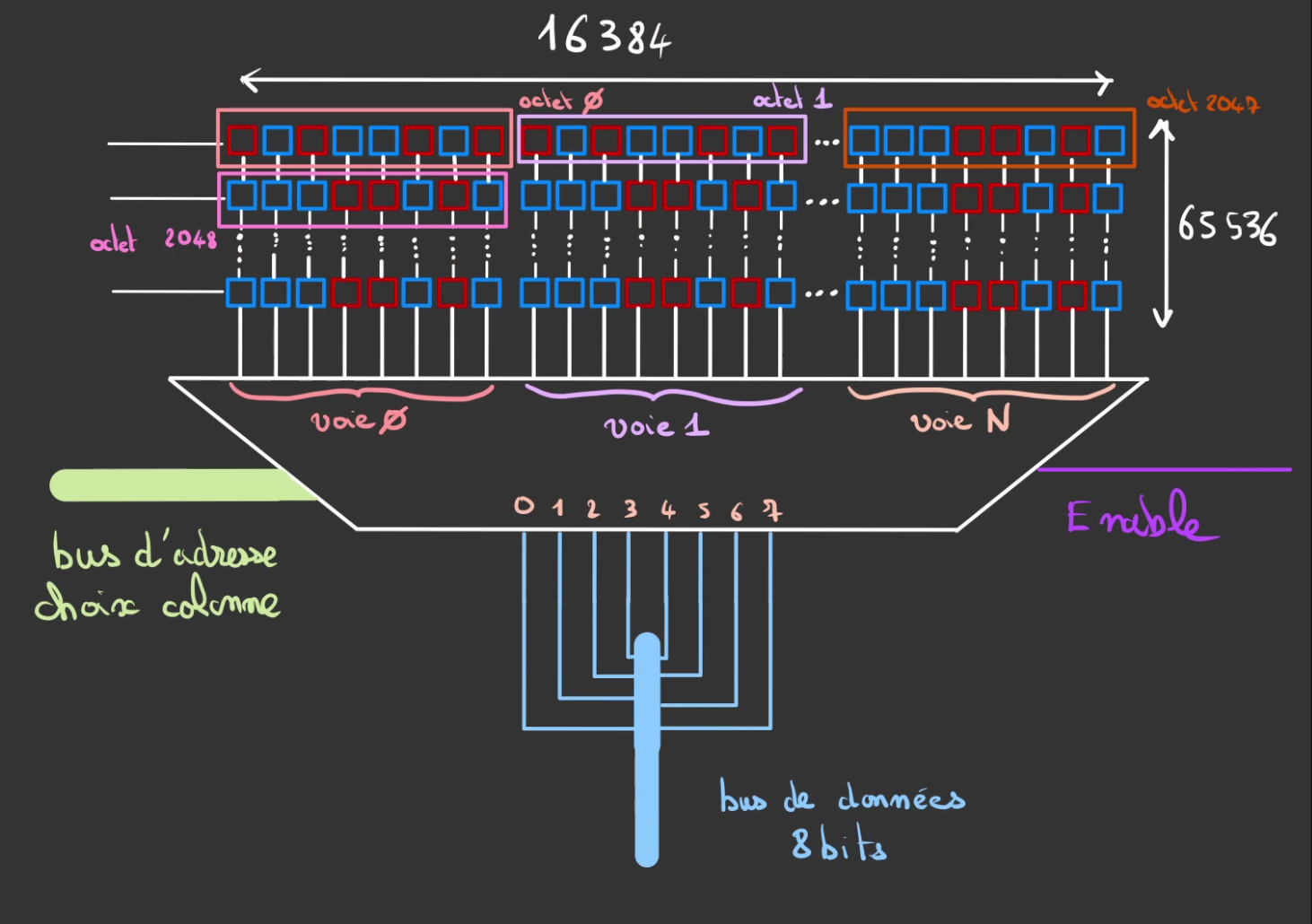

On a ainsi des matrice de largeur multiple de 8. Ici 16384. Ce qui donne 16384 / 8 = 2048 octets par lignes multiplié par le nombre de lignes, ici 65536, ce qui donne 2048 * 65536 = 134217728 adresses où 128 Mo.

On complexifie le Mux/DeMux mais l'on divise par 8 le nombre de decodeur de lignes nécessaire !

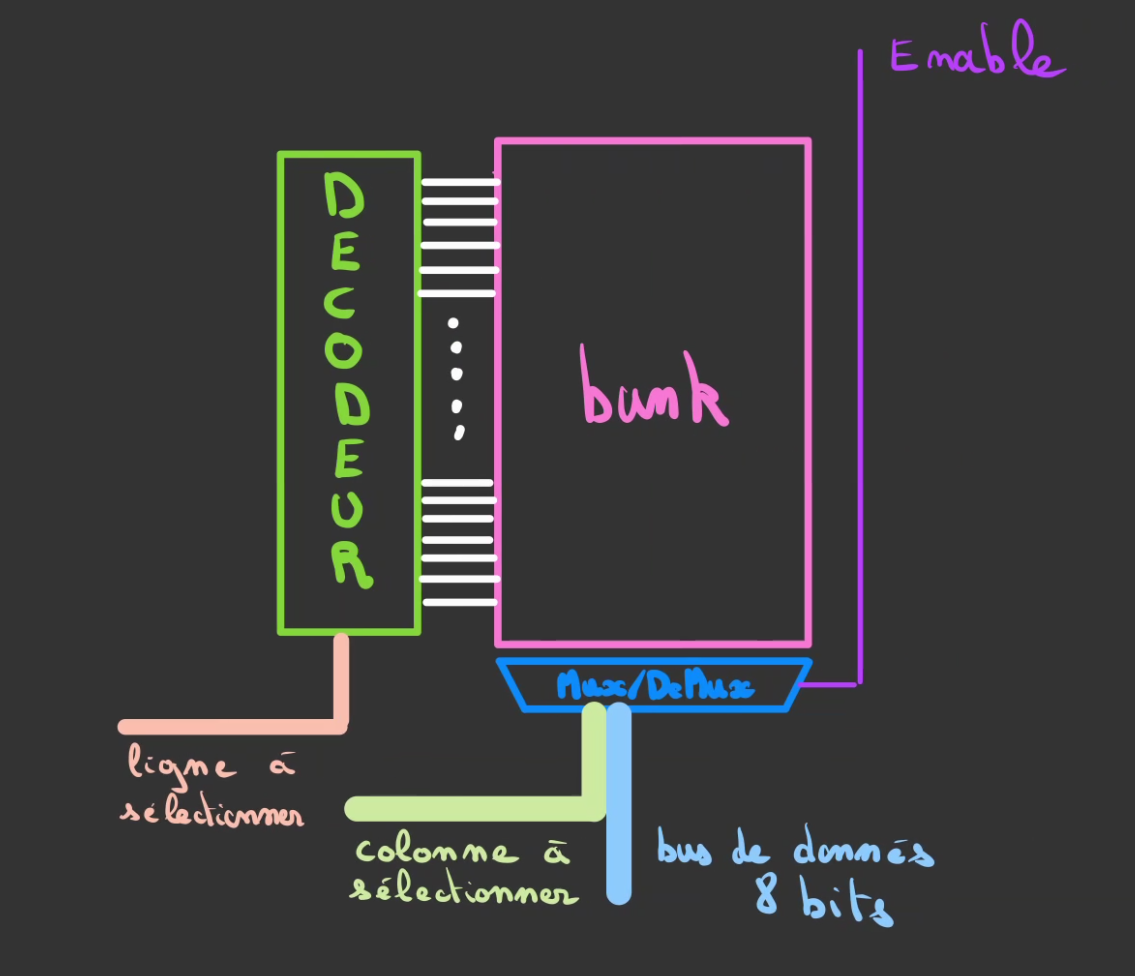

Et de fait, cette bank a le même comportement qu'auparavant, nous avons un décodeur qui se charge de sélectionner la ligne dans la matrice de mémoire et un Mux/DeMux qui décode la colonne sélectionnée.

La différence est que l'on a un décodeur pour sélectionner un octet complet et plus seulement un bit. De même le Mux/DeMux est lié à un octet complet.

Cette optimisation provoque une différence fondamentale: l'unité de base de la mémoire n'est plus le bit mais l'octet. De fait, il n'est plus possible d'écrire ou de lire un bit spécifique, seulement le paquet de 8 qu'il contient.

On peut alors agencer tout ce beau monde dans le chip pour stocker notre octet.

Et en étant intelligent dans le placement on peut mettre le nombre que l'on désire de banks.

De cette manière on minimise l'utilisation de composants onéreux comme les décodeurs et on maximise le nombre de cellules mémoires pour plus de stockage !

Il existe aussi tout un tas d'optimisations lié au fait que l'on puisse lire plusieurs banks en même temps et donc créer des files d'entrées/sorties, mais je vais être honnête avec vous, j'ai pas tout compris ^^'

Donc on va s'arrêter là 😄

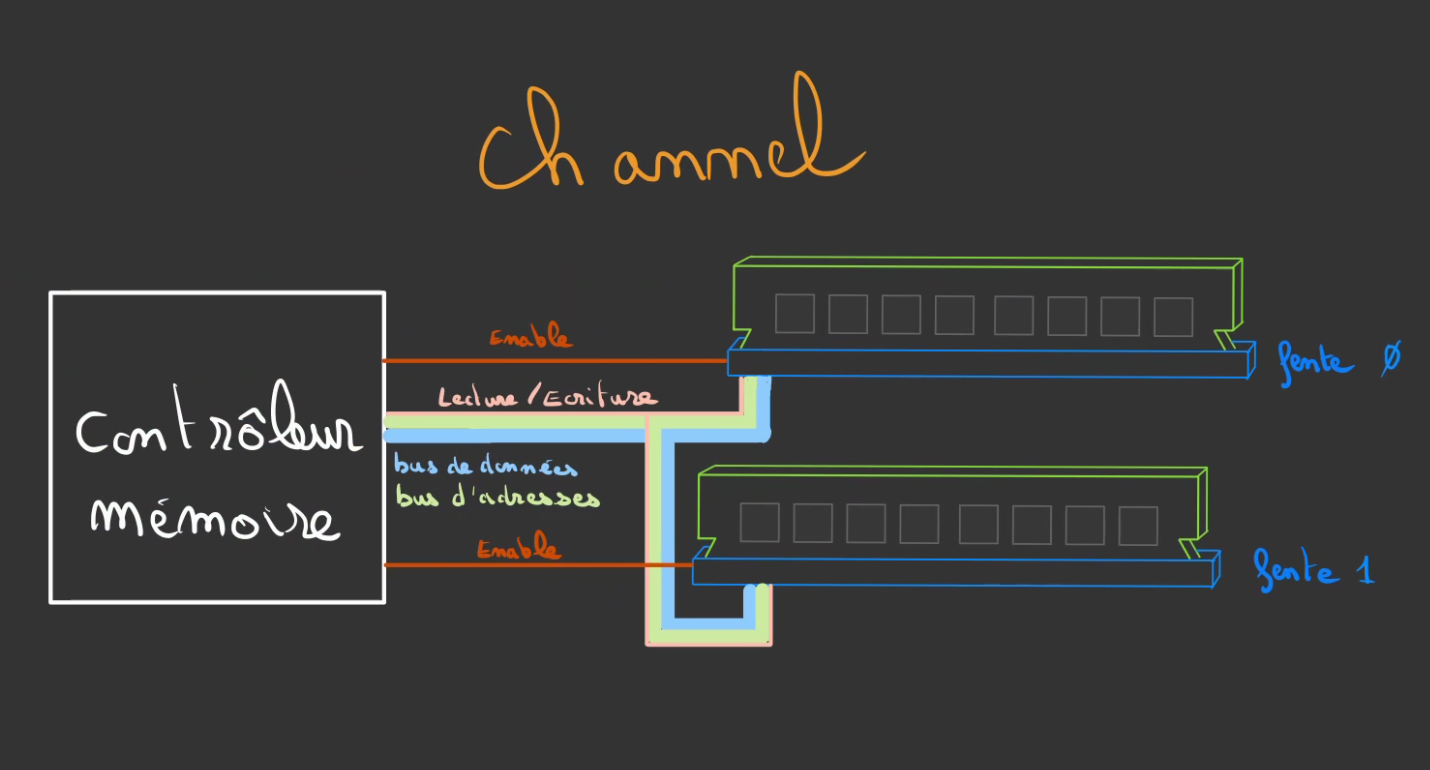

Channel

Dernière chose avant de se quitter.

Une barrette de RAM c'est cool mais pour les plus grosses dans le commerce on tourne aux alentours de 8Go / 16Go. Sauf que pour lancer des monstres comme Cyberpunk 2077, il faut déjà 8Go. Il ne va pas rester grand chose pour le reste du système ^^'

Du coup dernière pièce du puzzle.

On va brancher plusieurs barrette de RAM qui commenceront toutes à l'adresse 0.

Mais on va les rattacher à un composant, un contrôleur mémoire qui va se charger de mapper les addresses suppérieures à la taille de la RAM sur la seconde barette par exemple. Ce qui permet avec des barettes de 8Go de créer des octets à des adresses à 15Go ou plus.

On va alors brancher un unique bus d'adresses, bus de données et bus de contrôle (lecture/écriture). Puis avec un fil d'activation unique à la barrette de RAM décider de quelle barette on souhaite choisir le paquet de 64 bits.

On a donc une barette de RAM dans chaque fente.

Et on branche tout le monde sur le contrôleur mémoire.

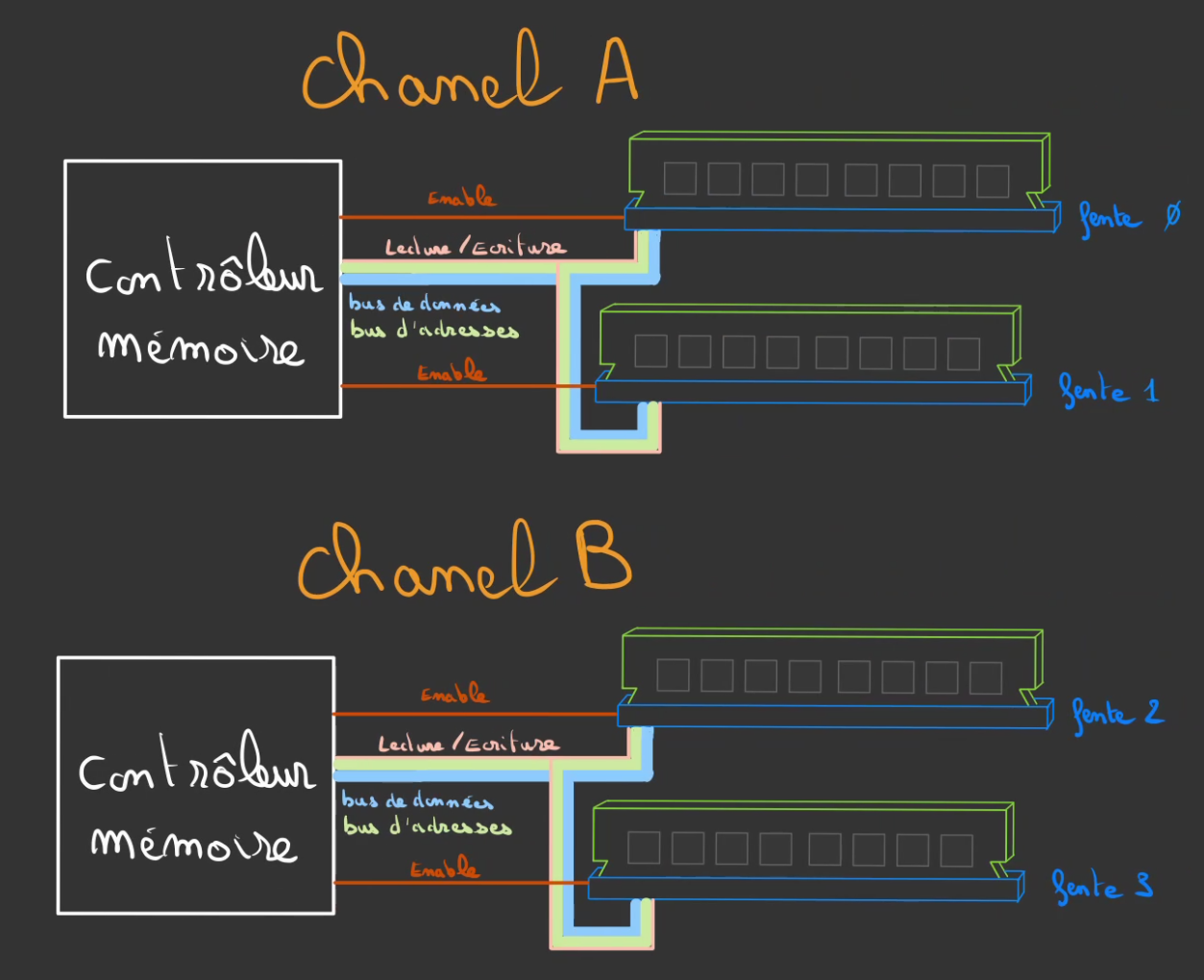

On peut alors généraliser le système de channel.

Ici, un channel A et un channel B. Chaque channel gérant 16Go de mémoire qui mis ensemble créé un bloc unifié de 32Go adressables !

Il existe des barettes de RAM dual channels, ce qui signifie que channels sont rattaché à chaque barettes de RAM.

On a aussi la possibilité de scinder un channel de 64 bits en deux channels de 32 bits, et ainsi pouvoir parralléliser encore plus d'action, c'est ce qui est par exemple utiliser dans la technologie DDR5.

Le nombre de channel est généralement limité à 2 car il est très onéreux de mettre en place un channel, sur les technolgies modernes ça représent 288 fils ! 288 fils qui faut réussir à placer sur la carte mère sans qu'ils ne se croisent ni n'intèfèrent entre eux. Il y a également des contraintes sur la longueurs des fils.

Ils doivent tous être de la même longeur, sinon les signaux du bit 1 du bit12 serait désynchronisés et quand on est dans des fréquences de plusieurs GHz, le moindre micro-mètre voir nanomètre de trajet supplémentaire peut avoir des conséquences.

C'est pour toutes ces raisons que l'on tente à tout prix d'augmenter la taille des barettes de RAM et non le nombres de slots sur la carte-mère.

Un channel n'a pas besoin que ses deux fentes soient remplies, par contre si c'est le cas, les barettes doivent être identiques !

Conclusion

J'espère que cette petite introduction au principe de fonctionnement vous aura plus, ce n'est évidemment pas un cours, j'ai pris des raccourci que même sur Mario Kart on ne prendrait pas.

J'ai également passé sous silence l'aspect dynamique du système qui aurait demander beaucoup trop temps à expliquer dans un article écrit.

Ma volonté quand j'ai écrit ce post était de moi-même comprendre comment ça marchait.

J'espère ne pas avoir dit trop de bêtises, le sujet est très vaste, j'ai fait de mon mieux pour vulgariser sans trop déformer la réalité.

A la prochaine fois pour un nouvel article sur autre chose ❤️

Ce travail est sous licence CC BY-NC-SA 4.0.